520.492 Mixed-Signal VLSI Systems

Week 3

## **Memory and Arithmetic**

## References

- 1. Geiger, Allen and Strader: pp. 821-866.

- 2. Weste and Eshraghian (2<sup>nd</sup> Ed.), Chapter 8.

## MEMORY AND ARITHMETIC

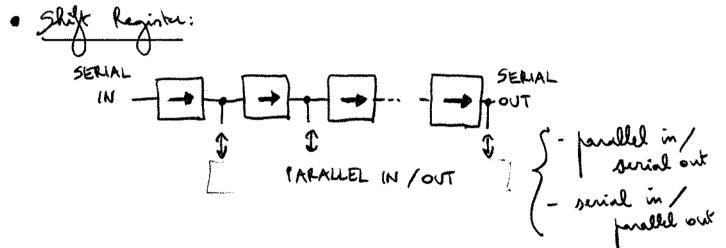

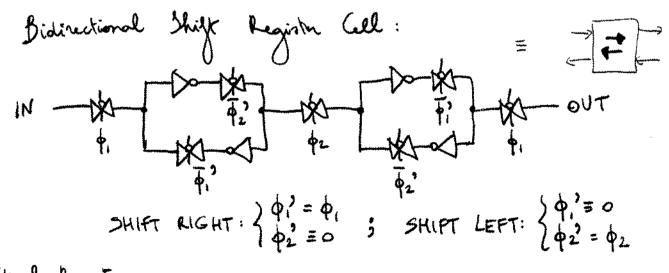

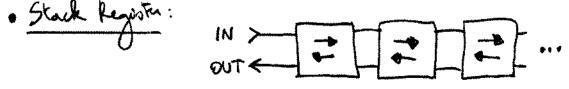

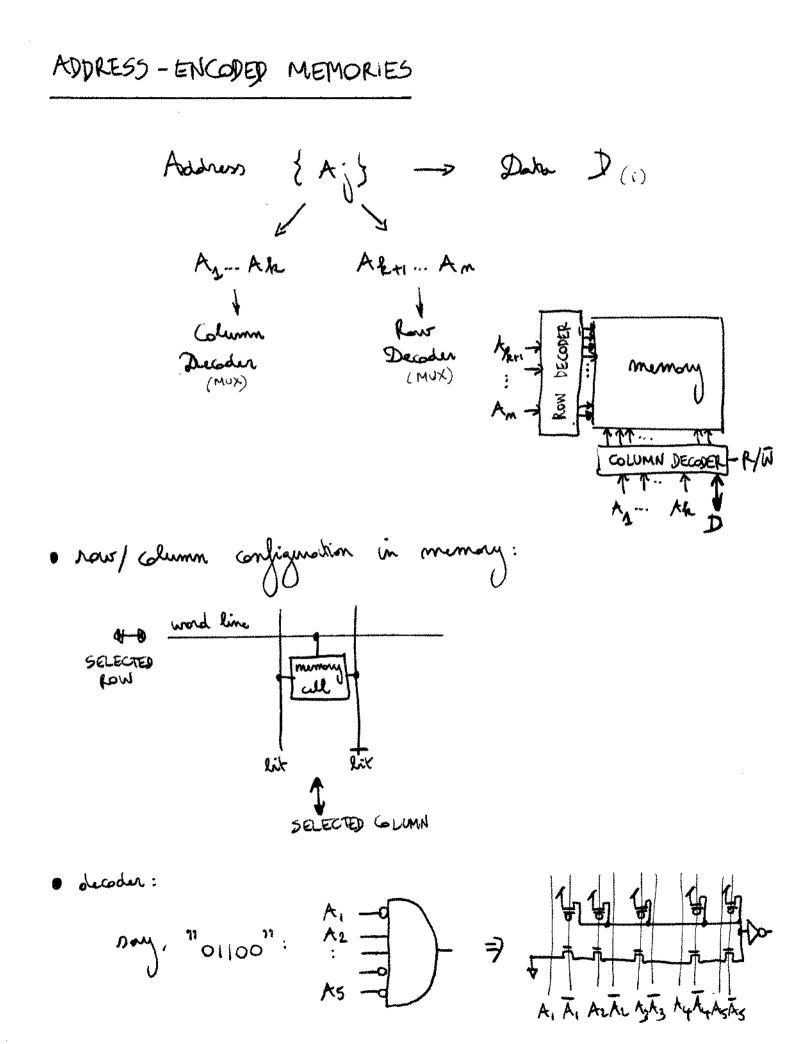

## REGISTERS

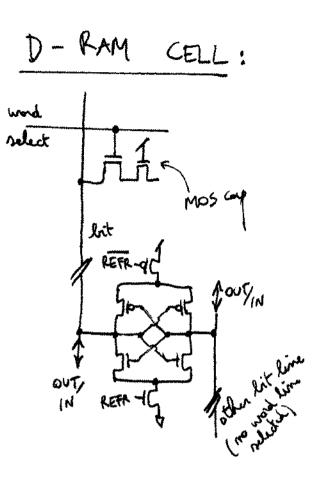

3T DRAM

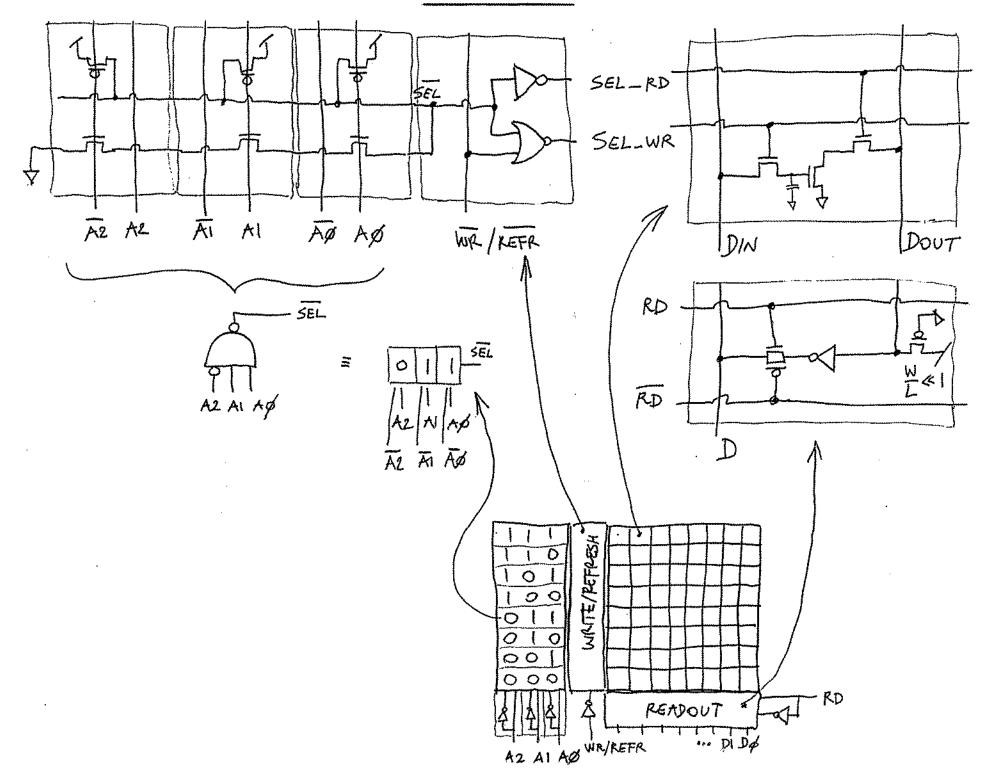

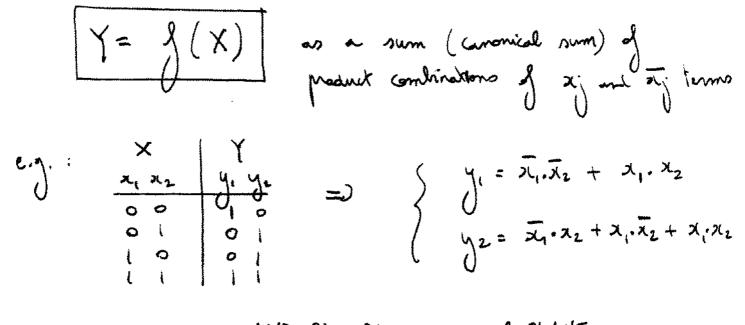

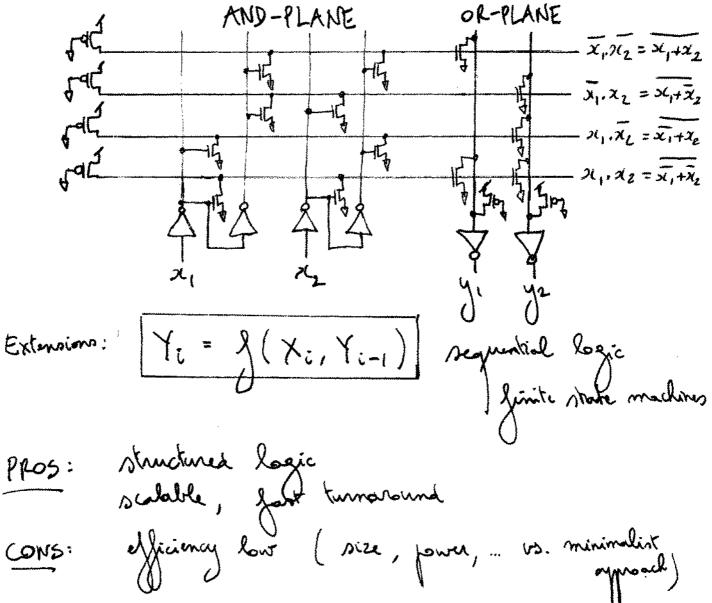

PROGRAMMABLE LOGICAL ARRAYS (PLA)

$$\frac{ADDITION}{A = \sum_{i=0}^{n-1} A_i 2^i} A_i 2^i S = A + B = \sum_{i=0}^{n-1} (A_i + B_i) 2^i$$

$$B = \sum_{i=0}^{n-1} B_i 2^i S = A + B = \sum_{i=0}^{n-1} (A_i + B_i) 2^i$$

$$= \sum_{i=0}^{n-1} S_i 2^i$$

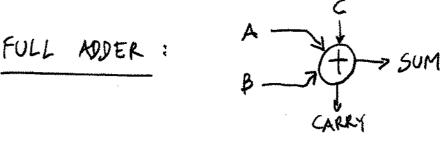

$$\begin{cases} S_i = (A_i + B_i + C_i) \mod 2 \\ (C_{i+1} = (A_i + B_i + C_i) \text{ div } 2 \\ (anithmetric) \end{cases}$$

| Ai | Ďc | Ci | $ (A_i+b_i+C_i) $ | Si | Giti |                                         |

|----|----|----|-------------------|----|------|-----------------------------------------|

| 0  | 0  | ø  | 9                 | 0  | 0    |                                         |

| 0  | 0  | ١  | 1                 |    | 0    | G-ADBOC                                 |

| 0  | l  | ٥  | t                 |    | 0    | $S_i = A_i \oplus B_i \oplus C_i$       |

| 0  | l  |    | 2                 | 0  |      |                                         |

| 1  | 0  | ø  | ۱ (               |    | 0    | $C_{i+1} = A_i B_i + A_i C_i + B_i C_i$ |

| l  | 0  | 1  | 2                 | ø  | ١    |                                         |

| l  | l  | 9  | 2                 | 0  | -    | ( logic)                                |

| ł  | ł  | I  | 3                 |    | 1    | 0                                       |

•

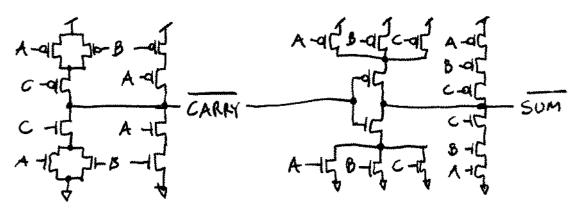

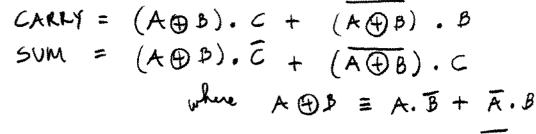

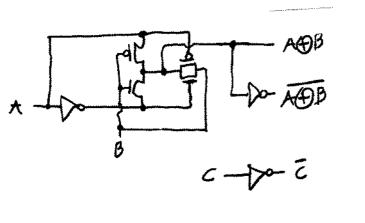

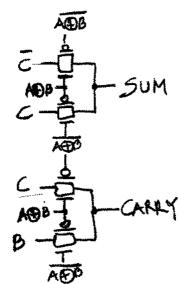

(1) CARRY = A.B + C.(A+B)  $a_{inverselie}(G)$   $p_{inverselie}(P)$   $SVM = ABC + ABC + \overline{ABC} + \overline{ABC} =$  $A.B.C + (A+B+C). \overline{CARRY}$

(2)

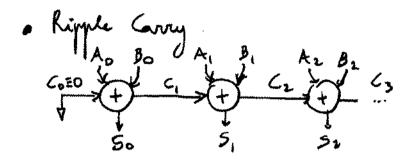

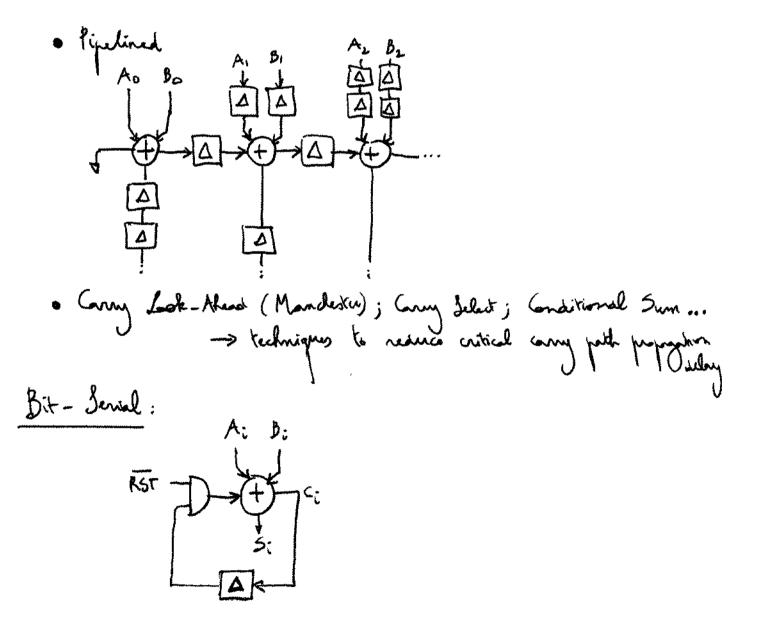

Bit- Parallel:

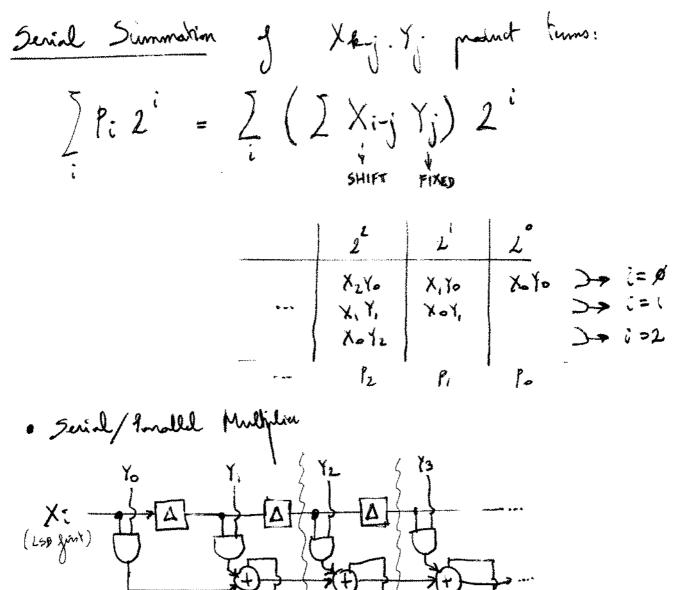

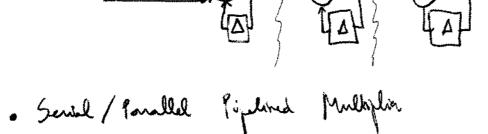

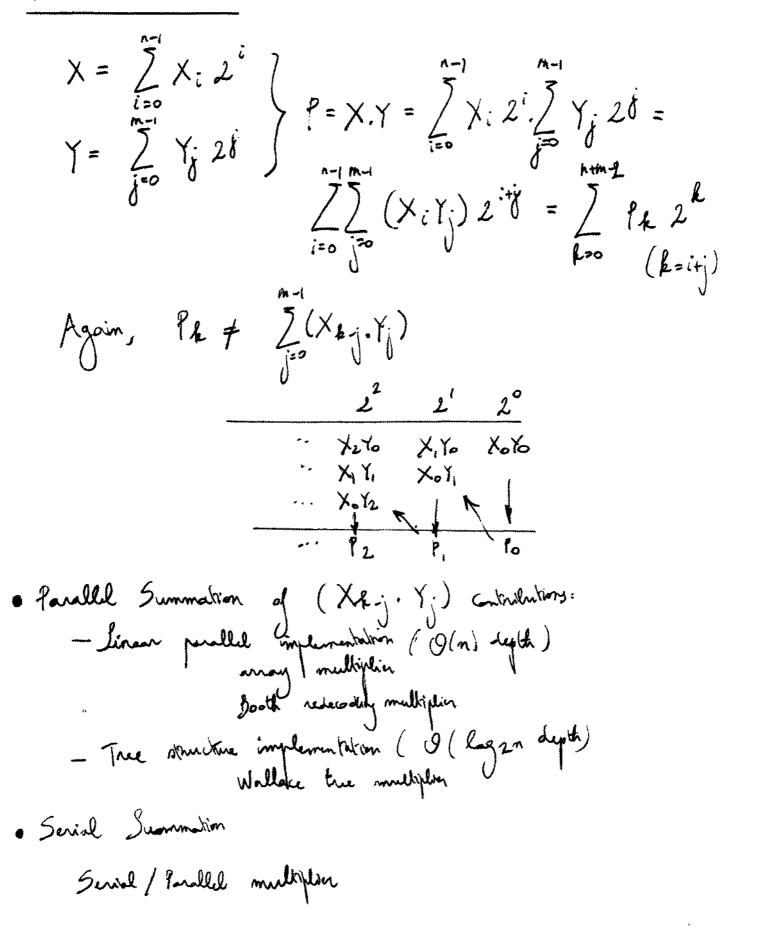

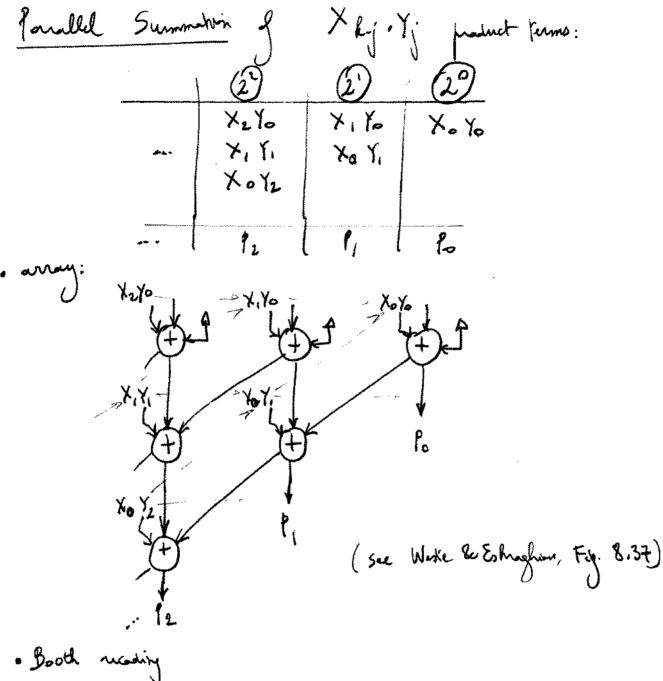

MULTIPLICATION

. True structure ( linony, log 2 (n) lating)