# Dynamic MOS Sigmoid Array Folding Analog-to-Digital Conversion

#### Roman Genov and Gert Cauwenberghs

Abstract—A dynamic, saturating difference circuit for large-scale parallel folding analog-to-digital conversion is presented. The circuit comprises a subthreshold nMOS transistor source-coupled to a capacitor, implementing a log-domain integrator. The output current is a logistic sigmoidal function of the change in voltage on the gate. Offset and gain of the differential sigmoid are controlled by timing of global clock signals and are independent of transistor mismatch. Folding operation for analog-to-digital conversion is obtained by differentially combining and integrating currents from a bank of sigmoid units. A 128-channel parallel bank of 4-bit Gray-code folding analog-to-digital converters measures 0.75 mm  $\times$  2 mm in 0.5  $\mu$ m CMOS and delivers 768 Msps at 82-mW power dissipation.

*Index Terms*—Charge-mode comparator, correlated double sampling, diode integrator, folding analog-to-digital converter (ADC), interpolating ADC, sigmoid.

## I. INTRODUCTION

High-performance data conversion can be achieved either by expending power and area to achieve high precision in a single analog architecture or by distributing the architecture over multiple low-resolution quantization tasks, each implemented with relatively imprecise analog circuits, and combined in the digital domain. Delta-sigma modulation has proven to be superior in attaining very high precision by distributing the quantization process over time [1]. Both high speed and high resolution can be achieved by distributing the quantization process in space [2].

The highest speeds in analog-to-digital conversion are obtained with flash and folding converter architectures. A folding analog-to-digital converter (ADC) compared to a flash ADC offers fewer comparators and reduced decoding logic, thus allowing higher speed at lower power [3]. A folding interpolating ADC further interpolates the folded output signals to increase resolution or reduce folding rate in a multistage conversion architecture.

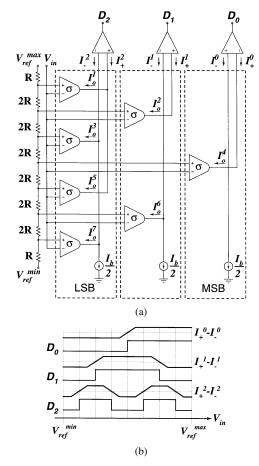

Fig. 1(a) depicts an example 3-bit folding ADC [4], [5]. Each of the three folding circuits comprises identical saturating difference units at linearly spaced inflection voltages, whose outputs are combined in alternating fashion. The folded output signals are zero-thresholded by high-gain comparators, producing Gray-code outputs illustrated in Fig. 1(b). The comparator outputs are latched and digitally postprocessed to generate binary-coded outputs.

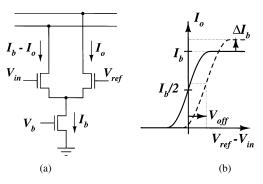

Conventionally, the saturating difference unit ( $\sigma$ ) of a folding circuit is implemented as a bipolar junction transistor (BJT) or MOS differential pair. The differential output current is a saturating monotonic smooth (sigmoid) function of the differential input voltage. For instance, in the case of a MOS differential pair shown in Fig. 2(a) and

Manuscript received January 15, 2003; revised August 27, 2003. This work was supported by NSERC 261606-0, ONR N00014-99-1-0612, and the National Science Foundation under Grant NSF IIS-0209289. This paper was recommended by Guest Editors A. Rodríguez-Vázquez, F. Mediero, and O. Feely.

R. Genov is with the Department of Electrical and Computer Engineering, University of Toronto, Toronto, ON M5S 3G4, Canada (e-mail: roman@eecg.toronto.edu).

G. Cauwenberghs is with the Department of Electrical and Computer Engineering, Johns Hopkins University, Baltimore, MD 21218 USA (e-mail: gert@jhu.edu).

Digital Object Identifier 10.1109/TCSI.2003.821304

Fig. 1. A 3-bit Gray-code folding ADC. (a) Architecture. (b) Folding currents and thresholded Gray-code output.

biased in the subthreshold region, one of the complementary output currents can be expressed as [6], [7]

$$I_o = I_b \sigma \left( A (V_{\rm ref} - V_{\rm in}) \right) \tag{1}$$

where  $I_b$  is the bias tail current,  $A = \kappa/V_t$  is a voltage range factor set by the Boltzmann thermal voltage  $V_t = kT/q$  and gate coupling coefficient  $\kappa$ , and

$$\tau(x) = \frac{1}{1 + e^{-x}} \tag{2}$$

is the canonical logistic sigmoid function.

Ì

The complementary output currents are differentially combined, with alternating polarity, to construct the folded output current illustrated in Fig. 1(b). Proper folding operation relies on precise addition and subtraction of sigmoid functions with identical saturation level  $I_b$  and with linearly spaced points of inflection  $V_{\rm ref}$ . MOS transistor mismatch in the differential pair and tail current supply contribute variability in the amplitude and offset of the implemented sigmoids, illustrated in Fig. 2(b). To maintain linearity in the ADC characteristic, relative variations in amplitude and offset cannot exceed the least significant bit (LSB) level (2<sup>-n</sup> for *n*-bit conversion). Offset and amplitude mismatch can be reduced through enlarged sizing of components, contributing power dissipation. Adaptive autozeroing techniques can compensate for offset [8], but not amplitude mismatch.

Fig. 2. (a) Conventional folding unit using a MOS differential pair. (b) Sigmoid differencing characteristic.

We present a compact, offset and amplitude-compensated folding circuit utilizing dynamic differential sigmoid ( $\sigma$ ) units, each implemented with one capacitor and four nMOS transistors. Section II describes the sigmoid difference unit, and Section III presents the folding circuit comprising these units. Section IV summarizes measured results from a densely integrated bank of 128 parallel 4-bit folding Gray-code ADCs fabricated in a 0.5- $\mu$ m CMOS process.

#### II. CORRELATED DOUBLE-SAMPLING SIGMOID UNIT

## A. MOS-C Diode-Integrator

This section demonstrates that a  $\sigma$  differencing and folding unit can be implemented using a single active element, with precisely controlled sigmoid amplitude and offset. The circuit consists of a capacitor and an exponential element, such as a diode [9] or a MOS transistor operating in the subthreshold regime [10], where the differential voltage is presented as a step in input voltage on the MOS gate. Offset compensation is achieved in the charge domain, similar to the CMOS charge-transfer comparator described in [11].

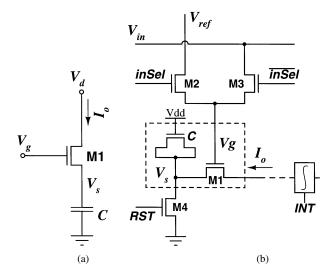

In the circuit of Fig. 3(a), the nMOS transistor is source-coupled to a capacitor. In the subthreshold and saturation regions, the drain current is exponential in gate and source voltage, and the large-signal dynamics of the integrator are described by

$$C\frac{dV_s}{dt} = I_o(t) = \frac{W}{L}I'_0e^{(\kappa V_g - V_s)/V_t}$$

(3)

which, by integrating over t and  $V_s$ , yields

$$CV_t e^{V_s/V_t} = \frac{W}{L} I'_0 e^{\kappa V_g/V_t} t + c_1 \tag{4}$$

with integration constant  $c_1$  as determined by initial conditions. Direct substitution yields

$$I_o(t) = \frac{CV_t}{t + \frac{c_1}{\frac{W}{T}I'_0 e^{\kappa Vg/V_t}}}.$$

(5)

At time t = 0, the input voltage is switched from  $V_g(0^-)$  to  $V_g(0^+)$ while the capacitor instantly retains the source voltage  $V_s(0)$ . The source current therefore switches from  $I_o(0^-)$  to  $I_o(0^+)$  over the transition at the gate as

$$I_{o}(0^{+}) = I_{o}(0^{-})e^{\kappa \Delta V_{g}/V_{t}}$$

(6)

where  $\Delta V_g = V_g(0^+) - V_g(0^-)$ . The output current (5) can thus be expressed in terms of initial conditions as

$$I_o(t) = \frac{I_o(0^+)}{\frac{I_o(0^+)}{CV_t}t + 1} = \frac{I_o(0^-)}{\frac{I_o(0^-)}{CV_t}t + e^{-\kappa \Delta V_g/V_t}}.$$

(7)

Interestingly, for  $t \gg CV_t/I_o(0^+)$ ,  $I_o(t)$  becomes independent of initial conditions [9]

$$I_o(t) \approx \frac{CV_t}{t}.$$

(8)

Fig. 3. (a) MOS-capacitor diode-integrator. (b) Dynamic sigmoid  $(\sigma)$  difference folding unit.

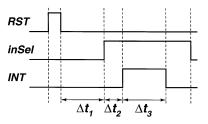

Fig. 4. Control signal timing diagram for the sigmoid  $(\sigma)$  difference unit circuit in Fig. 3(b).

# B. Differential Sigmoid Unit

Saturation of the output current of the circuit in Fig. 3(a) as a function of a change in the input voltage  $V_g$  is utilized in the design of the sigmoid difference unit as shown in Fig. 3(b). The nMOS capacitor is initially charged by pulsing reset (*RST*), as shown in Fig. 4. Over the time interval  $\Delta t_1$ , the capacitor discharges to raise  $V_s$  until M1 reaches well into the subthreshold region. The end of the interval defines the initial condition for the source current  $I_o(0^-)$ . The differential input voltage is presented as a transient on the gate,  $\Delta V_g = V_{\text{ref}} - V_{\text{in}}$ , implemented using an analog multiplexer M2 - M3 and controlled by inSel and  $\overline{inSel}$  timing signals in Fig. 4. In subthreshold,<sup>1</sup> this gate voltage transition produces a change in source current according to (7). By combining (6) and (7), the input–output characteristic of the sigmoid difference unit is expressed as

$$I_o(t) = I_{\text{sat}}(t) \sigma \Big( A(\triangle V_g - V_{\text{off}}(t)) \Big)$$

(9)

with the same logistic sigmoid function  $\sigma(.)$  and scale factor A as for the MOS differential pair in subthreshold (1), but with time-varying voltage offset and current amplitude

$$V_{\text{off}}(t) = -\frac{V_t}{\kappa} \log \frac{I_o(0^-) t}{C V_t} \approx -\frac{V_t}{\kappa} \log \frac{t}{\Delta t_1}$$

(10)

<sup>1</sup>For large values of  $\Delta V_g$ , the nMOS may initially enter the strong inversion region. This affects the timing but not the operation of the circuit, since once  $V_s$  has raised to reach the subthreshold the asymptotic relationship (8) holds again.

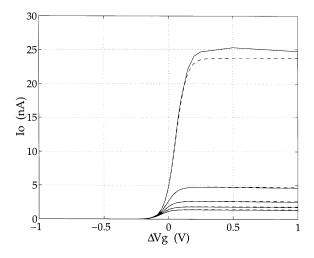

Fig. 5. The input-output characteristics of the MOS-C  $\sigma$ -unit at different fixed time intervals  $\Delta t_2$  after onset of *inSel*, calculated using (9) (dashed line) and simulated using Spectres for a 0.5- $\mu$ m CMOS process (solid line). Top to bottom:  $\Delta t_2 = 50, 250, 450, 650, \text{ and } 850 \text{ ns.}$

$$I_{\rm sat}(t) = \frac{CV_t}{t} \tag{11}$$

where the time origin t = 0 is taken at the onset of inSel (Fig. 4).

The time dependence of offset and amplitude is inconsequential to the folding characteristic, as time is in common to all  $\sigma$ -cells, and all currents are collected and integrated over the same time window,  $\Delta t_3$ (*INT*) in Fig. 4. Note that, by virtue of correlated double sampling in the differential transient  $\Delta V_g$  by switching M2 - M3, the offset  $V_{\text{off}}(t)$  is independent of M1 threshold variations and, to first order, 1/f noise. If desired, the residual uniform (systematic) offset can be eliminated by controlling the timing of  $\Delta t_2$  and  $\Delta t_3$  relative to  $\Delta t_1$ . In particular, at the onset of the *INT* integration interval  $(t = \Delta t_2)$ , the voltage offset (10) reduces to zero when  $\Delta t_2$  equals  $\Delta t_{1.2}^2$

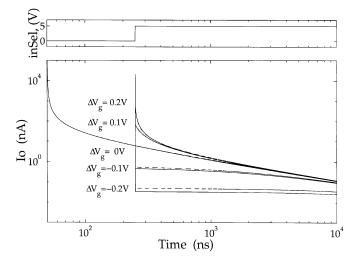

Fig. 5 illustrates the theoretical and simulated input–output characteristics of the  $\sigma$ -unit for different time intervals  $\Delta t_2$  after switching the inputs. Fig. 6 depicts transients in output current  $I_o$  for different values of  $\Delta V_g$ .

#### III. MOS-C FOLDING CIRCUIT AND GRAY-CODED FOLDING ADC

A dynamic Gray-coded folding ADC is realized by constructing folding circuits consisting of  $\sigma$  units just described. Folding circuits and comparators in the architecture of Fig. 1(a) combine to produce the Gray-coded output bits shown in Fig. 1(b). The folding currents could, in principle, be integrated for continued interpolating conversion to further increase resolution. For brevity in the present exposition, the interpolating functionality of the folding architecture for multistage ADC operation will not be elaborated on in what follows.

In general, an *n*-bit folding ADC comprises  $2^n - 1$  sigmoid units, arranged in *n* folding circuits, each folding circuit feeding into a single comparator to generate the Gray-coded bits  $D_j$ , j = 0, ..., n - 1. An additional sigmoid unit, supplying half the tail current  $I_{\text{sat}}/2$ , is needed in each folding circuit (*n* total) as a reference bias in the comparison.

Fig. 6. Differential sigmoid output current transients for different values of  $\Delta V_g$ . The solid line shows the SpectreS simulation results for a 0.5- $\mu$ m CMOS process; the dashed line was obtained using (9). The initial current  $I_o(0^-) = 6$  nA. The effective nMOS capacitor value is 45 fF.

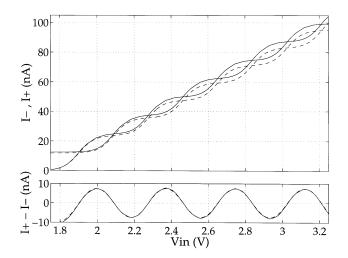

Fig. 7. Output currents of the LSB folding circuit for a 4-bit Gray-code ADC. The solid line represents the SpectreS simulation results for a 0.5- $\mu$ m CMOS process; the dashed line corresponds to (14) and (13). The time interval  $\Delta t_2 = 50$  ns.

#### A. MOS-C Folding Circuit

The  $\sigma$ -units produce output currents

$$I_o^i = I_{\text{sat}}(t) \sigma \left( A(V_{\text{ref}}^i - V_{\text{in}} - V_{\text{off}}(t)) \right)$$

(12)

with inflection points  $V_{\rm ref}{}^i$  equally spaced between  $V_{\rm ref}{}^{\rm min}$  and  $V_{\rm ref}{}^{\rm max}$ , obtained by linearly tapping a resistive line. The reference sigmoid supplying the current  $I_{\rm sat}(t)/2$  is identical to the other  $\sigma$ -units but with half the capacitance, C/2, and saturated by applying a step in voltage given by the conversion range  $V_{\rm ref}{}^{\rm max} - V_{\rm ref}{}^{\rm min}$ .

For instance, in a 4-bit (n = 4) Gray-code ADC, the LSB (j = 3) differential folding output currents contain the following eight sigmoid contributions:

$$I_{+}^{3} = I_{\text{sat}} \sum_{i=0}^{3} \sigma \left( A (V_{\text{ref}}^{4i+1} - V_{\text{in}} - V_{\text{off}}) \right)$$

(13)

<sup>&</sup>lt;sup>2</sup>This choice results in zero offset for folding ADC operation, assuming that the thresholding comparison of the folding output takes place primarily at the onset of the *INT* interval through a regenerative amplification process as described in Section III-B. In the interpolative mode of folding ADC operation, the folding current is integrated over the entire  $\Delta t_3$  interval of *INT* resulting in a broadened sigmoid with input-referred voltage offset  $V_{\text{off}} = -V_t/\kappa \log(\Delta t_2/\Delta t_1 \sqrt{1 + \Delta t_3/\Delta t_2})$ , which reduces to zero for  $\Delta t_3 = \Delta t_1^2/\Delta t_2 - \Delta t_2$ .

Fig. 8. Integrating sense-amplifying comparator.

$$I_{-}^{3} = I_{\text{sat}} \sum_{i=0}^{3} \sigma \left( A (V_{\text{ref}}^{4i+3} - V_{\text{in}} - V_{\text{off}}) \right) + \frac{I_{\text{sat}}}{2}.$$

(14)

Theoretical and simulated output currents of a 4-bit LSB folding circuit are plotted in Fig. 7 as a function of input voltage. In the actual implementation, two additional  $\sigma$ -cells are used to avoid side effects visible at the lower and higher ends of the conversion interval.

#### B. Integrating Sense-Amplifying Comparator

Bit decisions are made on integrated, differentially folded  $\sigma$ -unit currents using a correlated double sampling sense-amplifying comparator. As discussed in Section II-B, synchronous and properly chosen timing of control signals eliminates the offset  $V_{\text{off}}(t)$ .

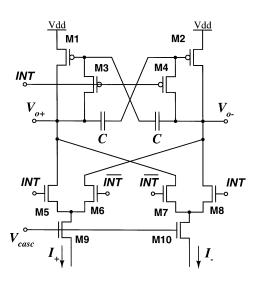

The integrating and latching sense-amplifying comparator is shown in Fig. 8. A cascode stage M9 - M10, controlled by the bias voltage  $V_{\rm casc}$ , provides low impedance input to the sense amplifier to improve the conversion speed and reduce the effect of the output conductance of the  $\sigma$ -cells. Current-domain correlated double sampling is achieved by swapping differential current inputs to the comparator at start of integration using multiplexers M5 - M6 and M7 - M8, from precharge to evaluate mode. In precharge mode (time interval  $\Delta t_2$  in Fig. 4) capacitors C are precharged through transistors M3 and M4 to the difference in gate voltages of transistors M1 and M2 set by currents  $I_{-}$  and  $I_{+}$ (including mismatch in threshold voltage). In evaluate mode (time interval  $\triangle t_3$  in Fig. 4), the multiplexers M5 - M6 and M7 - M8 switch the input currents. Positive feedback amplifies the difference in input currents, producing bistable voltage output. The correlated double sampling scheme compensates for comparator input-referred offset and doubles its input dynamic range. An additional comparator stage, not shown, further amplifies the difference  $V_{o+} - V_{o-}$  and latches the result.

## **IV. EXPERIMENTAL RESULTS**

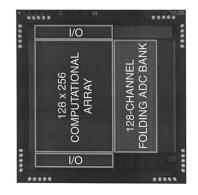

A prototype 128-channel bank of 4-bit dynamic Gray-codes folding ADCs was fabricated in a 0.5- $\mu$ m CMOS process. The die micrograph is shown in Fig. 9. The parallel bank of folding ADCs serves to quantize analog outputs from a massively parallel mixed-signal matrix–vector multiplying (MVM) computational array [13]. The ADC bank measures 0.75 mm × 2 mm, and dissipates 82 mW of power at 6-MHz clock, for a combined conversion rate of 768 Msps (7.68 × 10<sup>8</sup> samples per second). The portion of the power consumed by the folding

Fig. 9. Micrograph of a mixed-signal processor containing a computational array and a 128-channel parallel bank of 4-bit Gray-code folding ADCs. Die size is 3 mm  $\times$  3 mm in 0.5  $\mu$  m CMOS technology.

| TABLE I                           |

|-----------------------------------|

| FOLDING ADC ARRAY CHARACTERISTICS |

| Technology        | 0.5 μm 2P3M CMOS                     |

|-------------------|--------------------------------------|

| Size              | $0.7 \text{ mm} \times 2 \text{ mm}$ |

| Channels          | 128                                  |

| Resolution        | 4 bit                                |

| INL / DNL         | 0.5 LSB / 0.4 LSB                    |

| Conversion speed  | 768 Msps (128 $\times$ 6 Msps)       |

| Power dissipation | 82 mW at 5 V                         |

circuits (excluding sense amplifiers and output drivers) is 15 mW. The resistor string contributes 1 mW to total power. The measured characteristics are summarized in Table I.

In mixed-signal MVM array processing, multiple results from arrayparallel low-resolution folding ADCs are combined in the digital domain to digitize a single output vector component. Parallel use of multiple quantizers allows to boost overall quantization resolution by almost 2 bits beyond the resolution limits of each ADC channel [13], [14] to approximately 6 bits.

## V. CONCLUSION

A compact, offset and amplitude-compensated sigmoid differencing and folding circuit has been reported. Each sigmoid difference unit performs correlated double sampling of the inputs to avoid mismatch errors. The circuit operates in weak inversion and offers both high speed and low power. The design is suited for parallel data conversion on mixed-signal computational arrays, active pixel imagers, and other distributed charge or voltage mode circuits. A 128-channel parallel bank of 4-bit Gray-code folding ADCs converters has been implemented in a 0.5- $\mu$ m CMOS process, delivering  $128 \times 6$  Msps at 82-mW power dissipation.

The results are meant to illustrate the principle and not to indicate performance limits of the approach. Resolution can be enhanced using interpolation by integrating the folding currents onto capacitors and presenting the resulting differential voltage to subsequent folding stages. Speed is limited mainly by the time required for the MOS-C diode-integrators to enter the subthreshold region. It is straightforward to extend the circuit with BJTs, which attain exponential I-V characteristics at elevated current levels, for higher speed ADCs.

## REFERENCES

J. C. Candy and G. C. Temes, "Oversampled methods for A/D and D/A conversion," in *Oversampled Delta-Sigma Data Converters*. New York: IEEE Press, 1992, pp. 1–29.

- [2] A. G. W. Venes and R. J. van de Plassche, "Power and scaling rules of CMOS high-speed A/D converters," in *Analog Circuit De*sign. Norwood, MA: Kluwer, 1997, pp. 25–48.

- [3] —, "An 80-MHz 80 mW 8-b CMOS folding A/D converter with distributed track-and-hold preprocessing," *IEEE J. Solid-State Circuits*, vol. 31, pp. 1846–1853, Dec. 1996.

- [4] H. Kimura, A. Matsuzawa, and T. Nakamura, "A 10b 300 MHz interpolated-parallel A/D converter," *IEEE Trans. Circuits Syst. II*, vol. 44, pp. 65–85, Feb. 1997.

- [5] K. Ono, T. Matsuura, E. Imaizumi, H. Okazawa, and R. Shimokawa, "Error suppressing encode logic of FDCL in 6-bit flash A/D converter," *IEEE J. Solid-State Circuits*, vol. 32, pp. 1460–1464, Sept. 1997.

- [6] C. Mead, Analog VLSI and Neural Systems. Reading, MA: Addison-Wesley, 1989.

- [7] E. Vittoz, "Micropower techniques," in *Design of Analog-Digital VLSI Circuits for Telecommunications and Signal Processing*, 2 ed, Franca and Tsividis, Eds. Englewood Cliffs, NJ: Prentice-Hall, 1994, pp. 53–96.

- [8] M. H. Liu and S. I. Liu, "An 8-bit 10 MS/s folding and interpolating ADC using the continuous-time auto-zero technique," *IEEE J. Solid-State Circuits*, vol. 36, pp. 122–128, Jan. 2001.

- [9] R. Sarpeshkar, J. Kramer, G. Indiveri, and C. Koch, "Analog VLSI architectures for motion processing: From fundamental limits to system applications," *Proc. IEEE*, vol. 84, pp. 969–987, July 1996.

- [10] K. Boahen, "Retinomorphic vision systems," in Proc. 5th Int. Conf. MicroNeuro'96, 1996, pp. 2–14.

- [11] K. Kotani, T. Shibata, and T. Ohmi, "CMOS charge-transfer preamplifier for offset-fluctuation cancellation in low-power converters," *IEEE J. Solid-State Circuits*, vol. 33, pp. 762–769, May 1998.

- [12] M. Ismail and T. Fiez, Eds., Analog VLSI for Signal and Information Processing. New York: McGraw-Hill, 1995.

- [13] R. Genov and G. Cauwenberghs, "Charge-mode parallel architecture for matrix-vector multiplication," *IEEE Trans. Circuits Syst. II*, vol. 48, pp. 930–936, Oct. 2001.

- [14] —, "Algorithmic partial analog-to-digital conversion in mixed-signal array processors," in *Proc. IEEE Int. Symp. Circuits and Systems* (ISCAS'2003), Bangkok, Thailand, May 25–28, 2003.