#### 520.492 Mixed-Signal VLSI Systems

#### Prof. Gert Cauwenberghs

#### Week 1

#### **VLSI Technology and Device Characterization**

#### References

- 1. Geiger, Allen and Strader: pp 33-235.

- 2. Tsividis, Operation and Modeling of the MOS Transistor.

- 3. Sze, VLSI Technology.

- 4. Beynon & Lamb, "Charge Coupled Devices", in Topics in Applied Physics vol. 38.

### SILICON YLSI TECHNOLOGY

```

INGREDIENTS

Silicon

Polysilicon (POLY)

Oxtole (5102)

Impurities (diffusion, implants)

Mutal (Al, Au)

DEVICES

MOSFETS (nMOS, pMOS)

tipolars (npm, pmp)

Capacitors

refistors

+ derivates: phototransistors, floating gates, CCD's,...

LAYERS (typical MOSIS)

diffusion (n and p; marked with "Select")

metal (metal 1, metal 2, ...)

p-base (non vertical BJT in n-well process)

Serviced channel

+ contacts; via(5)

```

### MOS TRANSISTORS

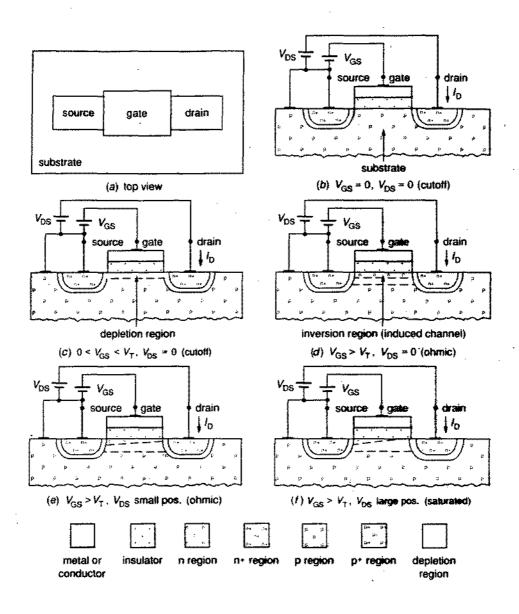

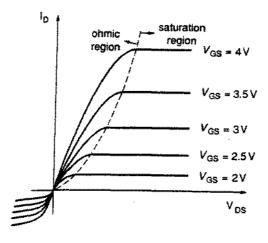

FIGURE 2.2-3

Typical output characteristics for an n-channel MOSFET.

Alove threshold: (Shichman - Hodges)

$$I_{D} = \begin{cases} \frac{1}{2} \kappa' \frac{W}{L} (V_{GS} - V_{T})^{2} (1 + \lambda V_{DS}) \\ \kappa' \frac{W}{L} (V_{GS} - V_{T} - \frac{V_{DS}}{2}) V_{DS} (1 + \lambda V_{DS}) \end{cases}$$

CUTOFF

SATURATION

OHM(C (TRIODE)

VT= VTO + 8 ( VØ-VBS-VØ)

Below thrushed:

$$I_D = I_o' \frac{V}{L} e^{\frac{kV_{GB} - V_{SB}}{V_{IK}}} \left(1 - e^{-\frac{V_{DS}}{V_{IK}}}\right) \left(1 + \lambda V_{DS}\right)$$

Vth = thermal vollage, ET (= 25 mV)

K = back gate effect

AC, small simple:  $C_{GD}$   $R_{D}$   $C_{BG}$   $V_{ga}$   $V_{ba}$   $G_{ab}$   $G_{ab}$

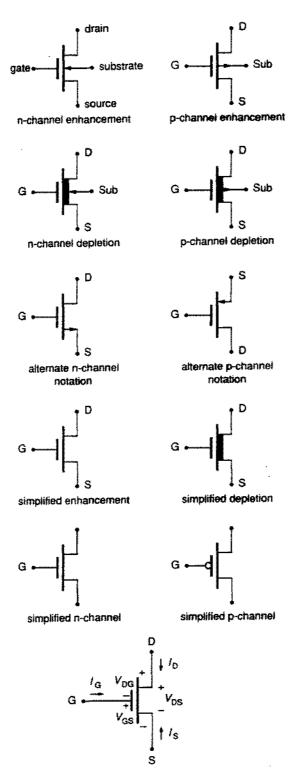

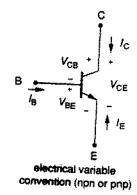

# Mos symbols;

electric variable convention (n- or p-channel, enhancement or depletion)

FIGURE 2.2-4

Symbols for MOS transistors.

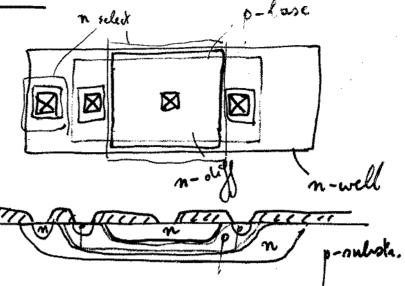

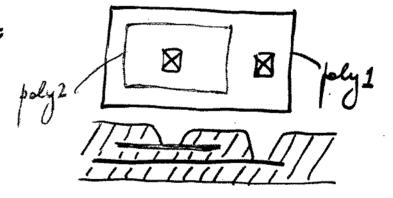

#### CIF:

#### Cross section;

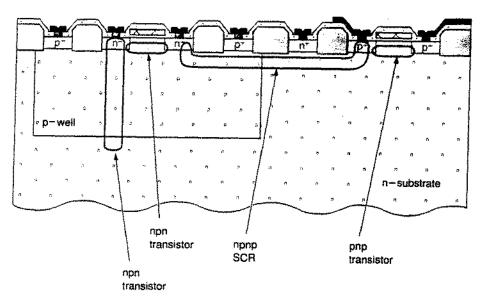

FIGURE 2.2-7

Parasitic transistors in a p-well CMOS process.

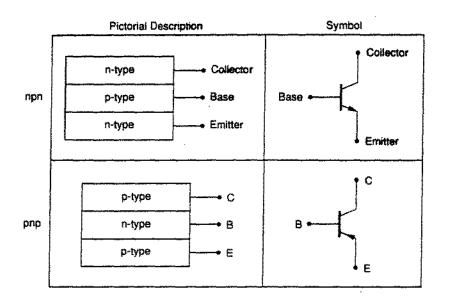

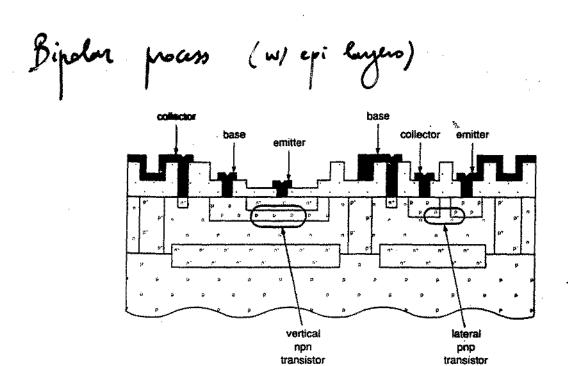

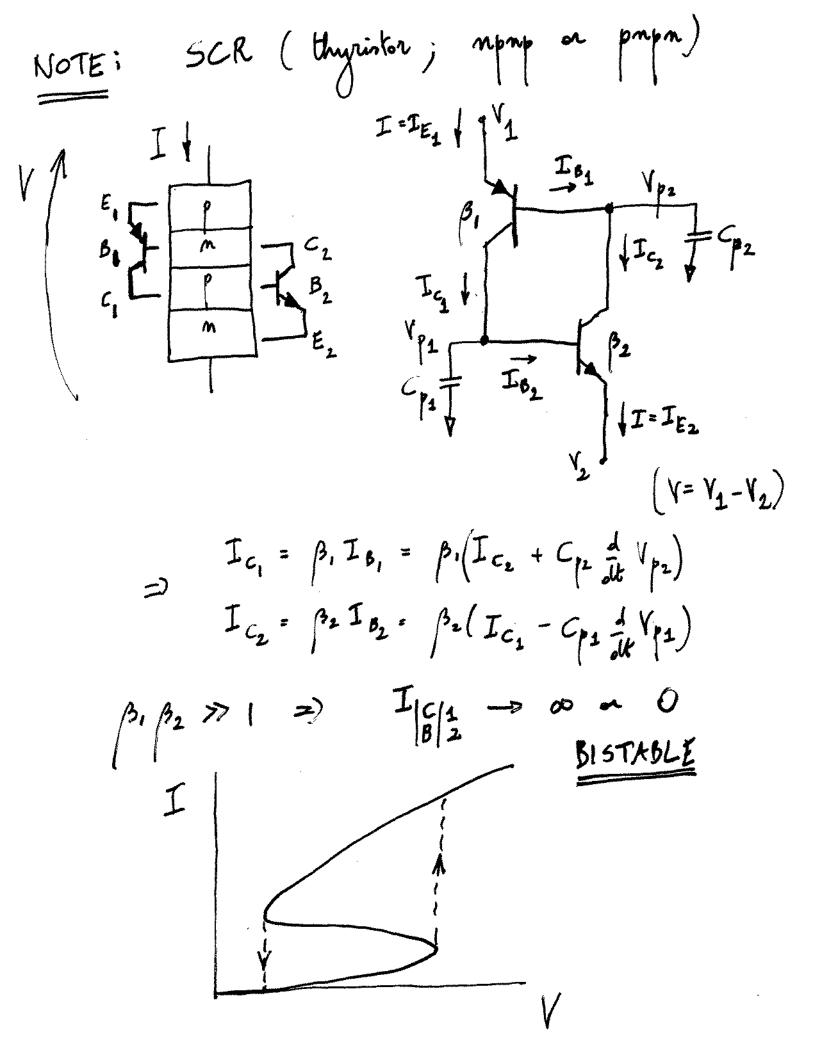

## BIPOLAR JUNCTION TRANSISTORS (BJT'S)

FIGURE 2.2-8

Bipolar transistors.

#### DC:

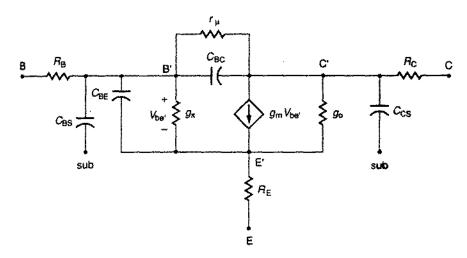

### AC:

FIGURE 3.3-12

High-frequency small signal equivalent circuit of BJT.

FIGURE 2.2-9

Vertical and lateral transistors in a bipolar process.

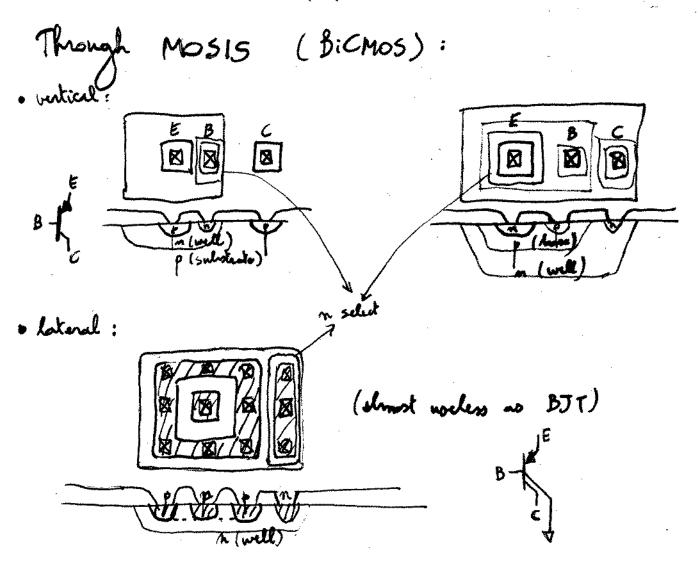

### COMPARISON

MO5

Bipolar

voltage-driven current source

Zin= 0

Zout = large

current-driven current source

Zin= small

Zout = large

ohmic insulation compact thermally stable

logic / memory (no static power)

suitched capacitors

low-noise precise matching fast

high speed withyling

linear analog

K

Bicmos YLSI

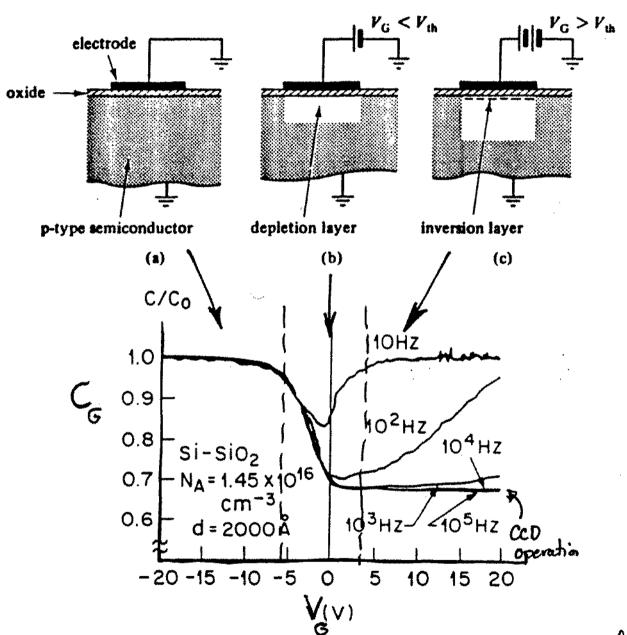

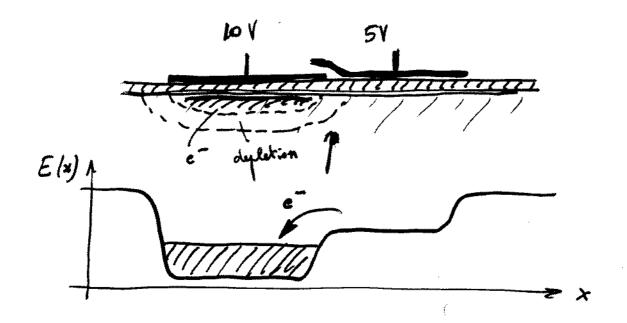

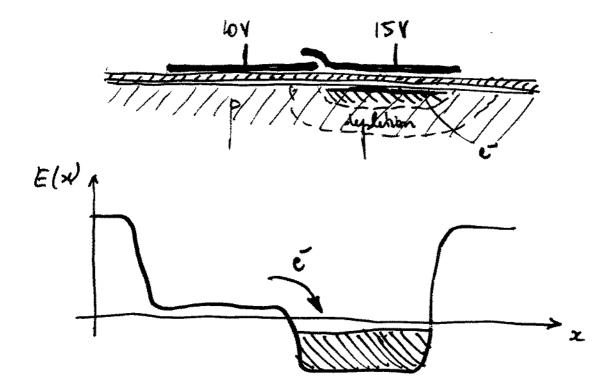

Slow recovery of inversion channel, unless there one drain on source obligations in contact with the channel to provide carriers fast.

## CCD'S (and CID'S)

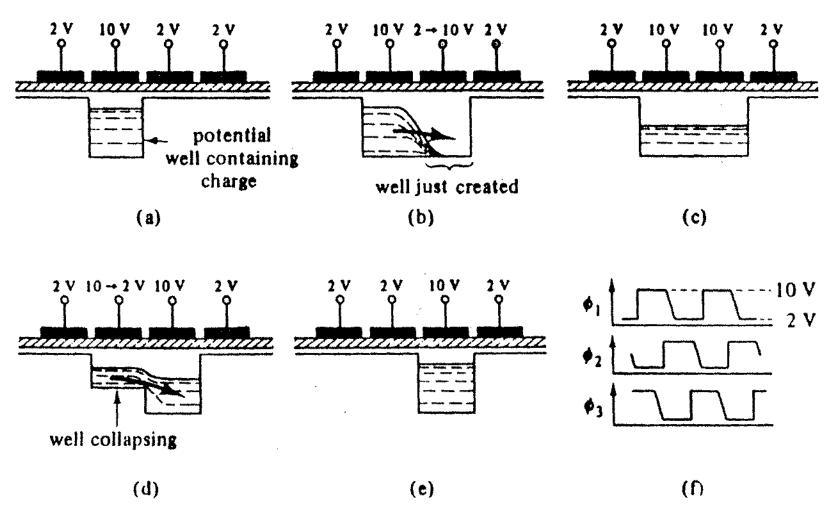

## Basic CCD Shift Register Operation

Fig. 1.7 (a)-(e) Movement of potential well and associated charge packet by clocking of electrode voltages; (f) clocking waveforms for a three-phase CCD.

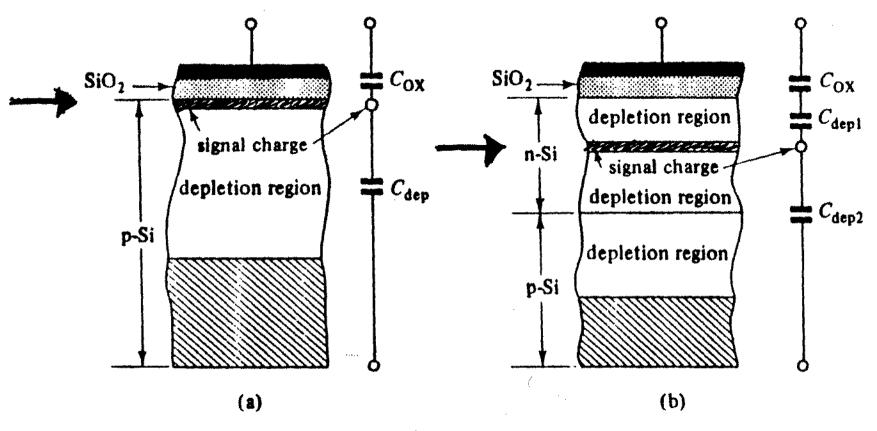

## Buried Channel CCD

TO REDUCE EFFECTS OF INTERFACE TRAIS BY PUSHING THE CARRIERS PURTHER BEZOW THE OXIDE INPUT DIODE **OUTPUT DIODE** +20V +20V TRANSFER ELECTRODES SiO2 -+15V 0٧ p-Si **EQUIPOTENTIAL LINES** TRANSFER CHANNEL

Same as surface channel CCD except for a weak n implant underneath the CCD gates.

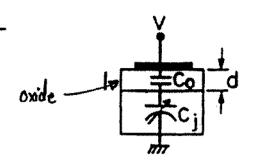

## Equivalent Capacitance of CCD's

Fig. 2.12 Capacitor equivalent circuits for (a) surface-channel and (b) buriedchannel CCDs.

SURFACE CHAWNEL

PRO: STANDARD CMOS TECH.

LINEAR Q(Y)

CON: . INTERFACE TRAPS

BURIED CHANNEL

PLO: • BETTER CHARGE TRANSFER EFF.

CON: . HIGHER VOLTAGES TO DRIVE

. NONLINEAR Q(V)

· EXTRA PROCESSING LAYER

- · phototransisters, photodiodes: same as BJTs, diodes ( base of the phototransister needs to be left floating to cellect photocurrent)

- · linear capacitors:

e linear resistors: poly strings (95HEET = 201/□)

HI-RES: 1000 1 / [] ( 0.5 mm AM15)