## BENG 216 Neuromorphic Integrated Bioelectronics

Week 1: Biophysical Foundations

Gert Cauwenberghs

Department of Bioengineering UC San Diego

http://isn.ucsd.edu/courses/beng216

## **BENG 216 Neuromorphic Integrated Bioelectronics**

| Date         | Торіс                                                                                                                                                                                                                                                                   |

|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 9/29, 10/1   | Biophysical foundations of natural intelligence in neural systems. Subthreshold MOS silicon models of membrane excitability. Silicon neurons. Hodgkin-Huxley and integrate-and-fire models of spiking neuronal dynamics. Action potentials as address events.           |

| 10/6, 10/8   | Silicon retina. Low-noise, high-dynamic range photoreceptors. Focal-plane array signal processing. Spatial and temporal contrast sensitivity and adaptation. Dynamic vision sensors.                                                                                    |

| 10/13, 10/15 | Silicon cochlea. Low-noise acoustic sensing and automatic gain control. Continuous wavelet filter banks. Interaural time difference and level difference auditory localization. Blind source separation and independent component analysis.                             |

| 10/20, 10/22 | Silicon cortex. Neural and synaptic compute-in-memory arrays. Address-event decoders and arbiters, and integrate-and-fire array transceivers. Hierarchical address-event routing for locally dense, globally sparse long-range connectivity across vast spatial scales. |

| 10/27, 10/29 | Midterm review. Modular and scalable design for neuromorphic and bioelectronic integrated circuits and systems. Design for full testability and controllability.                                                                                                        |

| 11/3, 11/5   | Low-noise, low-power design. Fundamental limits of noise-energy efficiency, and metrics of performance. Biopotential and electrochemical recording and stimulation, lab-on-a-chip electrophysiology, and neural interface systems-on-chip.                              |

| 11/10, 11/12 | Adaptive offset cancelation and autoranging in dynamic vision sensing. Tobi Delbruck's lecture on silicon retina history with a live demo of event-based dynamic vision systems.                                                                                        |

| 11/17, 11/19 | Learning and adaptation to compensate for external and internal variability over extended time scales. Background blind calibration of device mismatch. Correlated double sampling and chopping for offset drift and low-frequency noise cancellation.                  |

| 11/24, 11/26 | Energy conservation. Resonant inductive power delivery and data telemetry. Ultra-high efficiency neuromorphic computing. Resonant adiabatic energy-recovery charge-conserving synapse arrays.                                                                           |

| 12/1 - 12/5  | Project final presentations. All are welcome!                                                                                                                                                                                                                           |

## Lee Sedol vs. AlphaGo

Go World Champion vs. Google DeepMind ~ 100 W ~ 100 kW

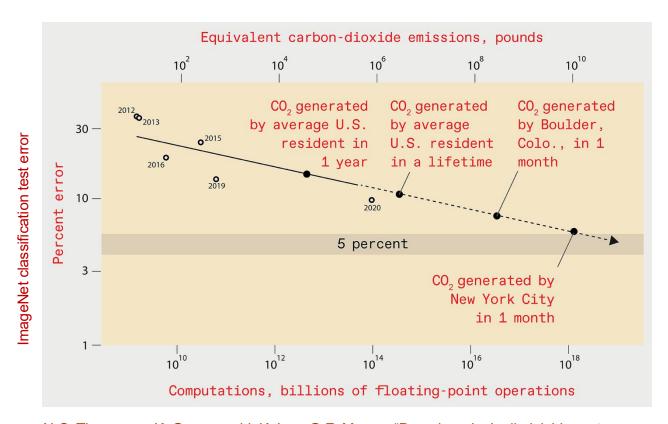

## **Steep Costs of Today's Deep Learning**

N.C. Thompson, K. Greenewald, K. Lee, G.F. Manso, "Deep learning's diminishing returns-The cost of improvement is becoming unsustainable." IEEE Spectrum, 24 Sept. 2021.

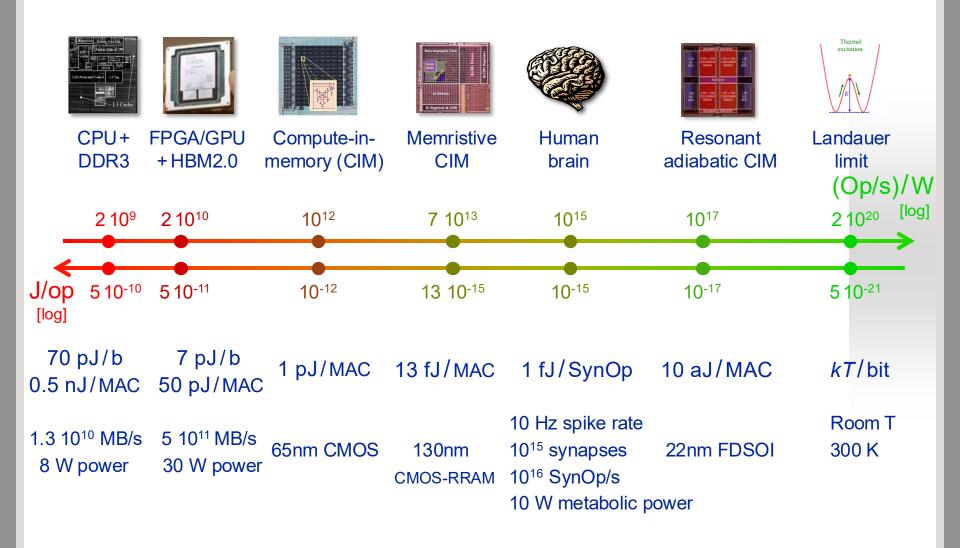

## **Energy Efficiency Spectrum**

## **Neuromorphic Engineering**

"in silico" neural systems design

Neuromorphic Engineering

Learning & Adaptation

## The Computer and the Brain

John von Neumann

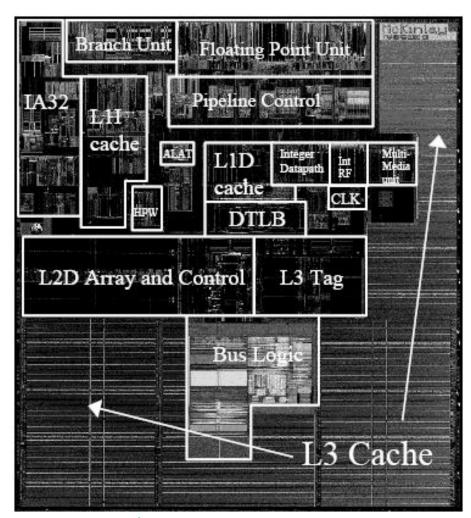

## One of History's Hottest CPU Microchips

#### Intel's Itanium 2

Source: IEEE ISSCC' 2002

#### The numbers ...

- 0.5 billion transistors in 120nm CMOS

- 1.6GHz clock, 64-bit instruction, 9MB L3 cache, 6.4GB/s I/O

- 2553 SPECfp\_base2000(30% faster than 2.8GHz P4)

- 130 Watts

#### ... and what they mean

#### Faster/cooler:

- Scientific computing

- Database search

- Web surfing

- Video games

What about intelligence?

## **Chips and Brains**

Itanium:

- $3 \cdot 10^9$  floating op/s

- 5 10<sup>8</sup> transistors

- 2 10<sup>9</sup> Hz clock

- $10^{10}$  Hz memory I/O

- 128-b data bus @ 400MHz

- 130 Watts

- Human brain:

- 10<sup>15</sup> synaptic op/s

- 10<sup>15</sup> synapses

- 1 Hz average firing rate

- 10<sup>10</sup> Hz sensory/motor I/O

- 10<sup>8</sup> nerve fibers

- 25 Watts

- Silicon technology is approaching the raw computational power and bandwidth of the human brain.

- However, to emulate brain intelligence with chips requires a radical paradigm shift in computation:

- Distributed representation in massively parallel architecture

- · Local adaptation and memory

- · Sensor and motor interfaces

- Physical foundations of computing

## **The Nanoscale Systems Revolution**

LOG<sub>2</sub> OF THE NUMBER OF COMPONENTS PER INTEGRATED FUNCTION

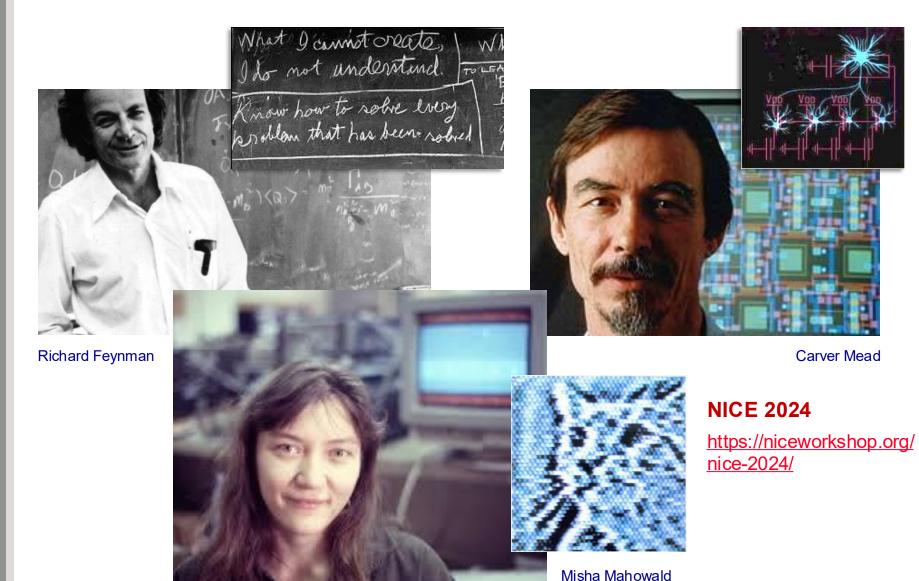

Richard Feynman

**Carver Mead**

Gordon Moore

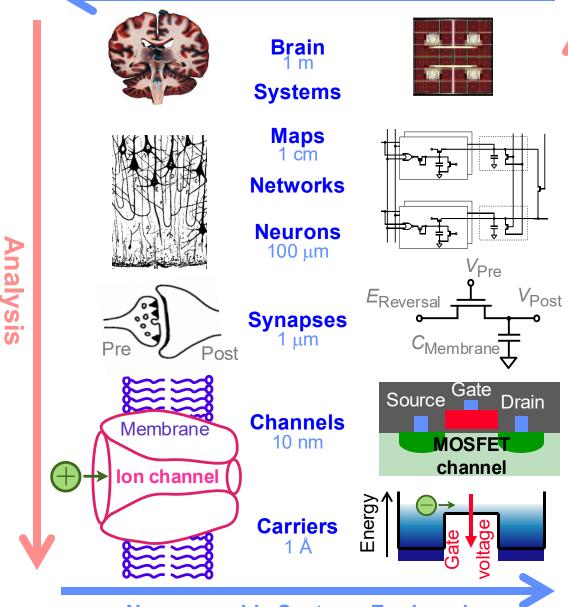

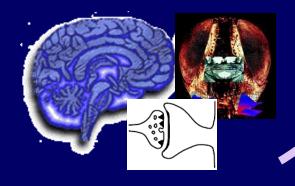

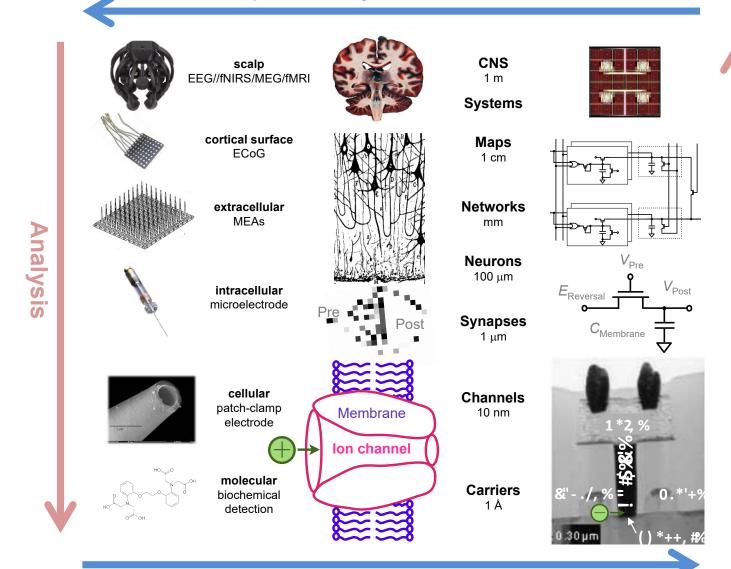

## **Analysis by Synthesis**

#### **Computational Systems Neuroscience**

# Synthesis

Multi-scale levels of investigation in analysis of the central nervous system (adapted from Churchland and Sejnowski 1992) and corresponding neuromorphic synthesis of highly efficient silicon cognitive microsystems. Boltzmann statistics of ionic and electronic channel transport provide isomorphic physical foundations.

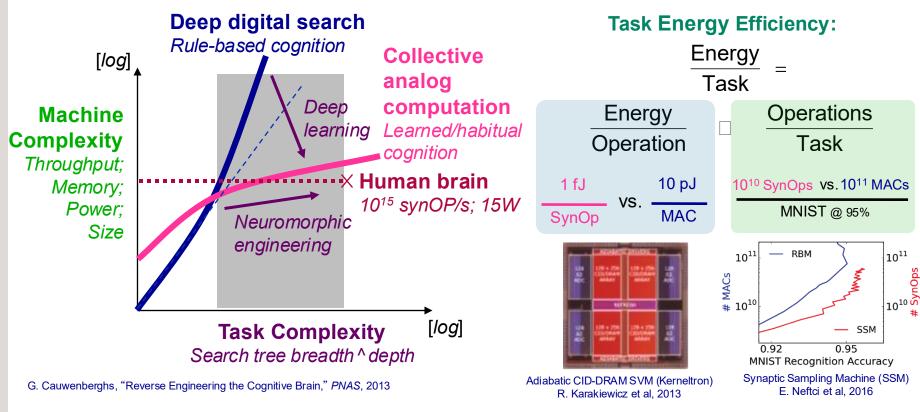

G. Cauwenberghs, "Reverse Engineering the Cognitive Brain," PNAS, 2013

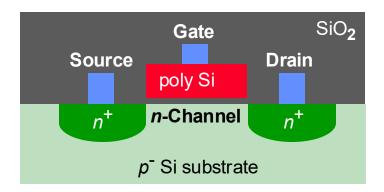

## **Physics of Computation**

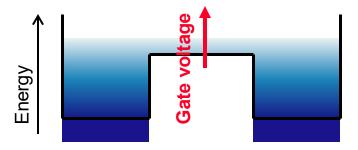

CMOS Silicon Technology

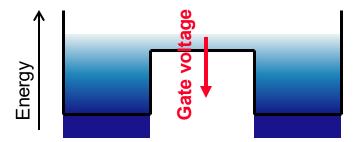

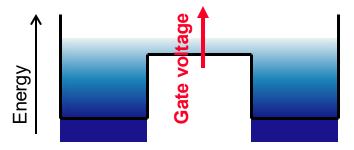

#### Voltage-dependent *n*-channel

- Electron transport between source and drain

- Gate controls energy barrier for electrons across the channel

- Boltzmann distribution of *electron energy* produces exponential *increase* in channel conductance with gate voltage

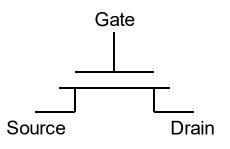

nMOS transistor circuit symbol

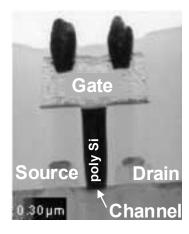

Cross-section of nMOS transistor in 0.18 µm CMOS process (Intel, 2002)

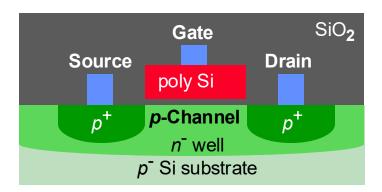

## **Physics of Computation**

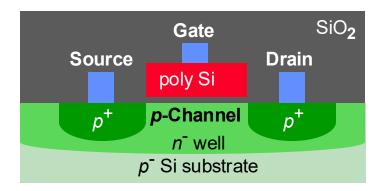

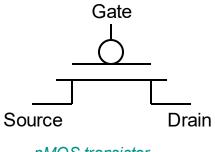

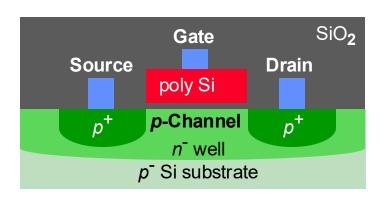

#### CMOS Silicon Technology

pMOS transistor circuit symbol

#### Voltage-dependent *p*-channel

- Hole transport between source and drain

- Gate controls energy barrier for holes across the channel

- Boltzmann distribution of hole energy produces exponential decrease in channel conductance with gate voltage

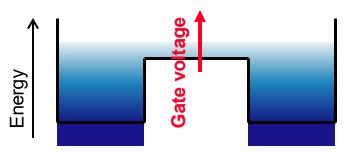

#### **Physics of Neural Computation**

#### Voltage-dependent p-channel

- Hole transport between source and drain

- Gate controls energy barrier for holes across the channel

- Boltzmann distribution of hole energy produces exponential decrease in channel conductance with gate voltage

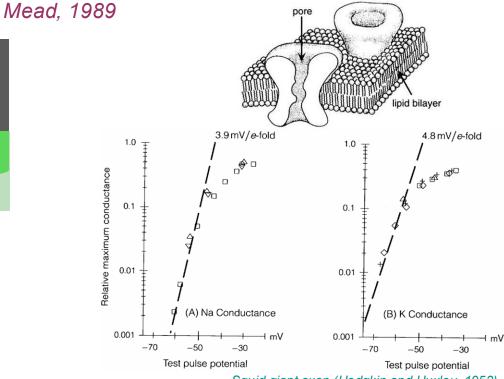

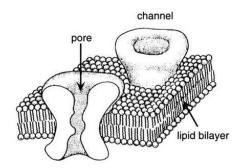

Squid giant axon (Hodgkin and Huxley, 1952)

channel

#### Voltage-dependent conductance

- K<sup>+</sup>/Na<sup>+</sup> transport across lipid bilayer

- Membrane voltage controls energy barrier for opening of ion-selective channels

- Boltzmann distribution of channel energy produces exponential increase in K<sup>+</sup>/Na<sup>+</sup> conductance with membrane voltage

#### **Physics of Neural Computation**

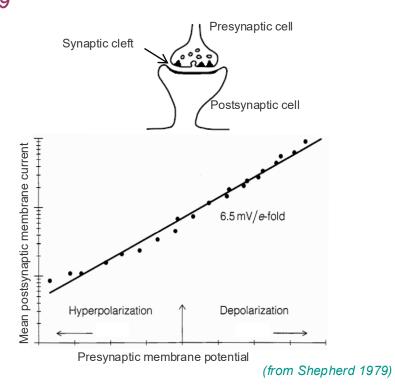

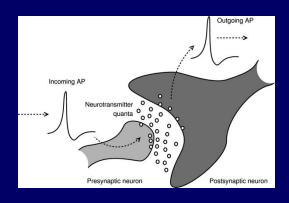

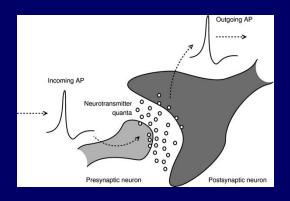

## Silicon and Biochemical Synapses Mead. 1989

#### Voltage-dependent p-channel

- Hole transport between source and drain

- Gate controls energy barrier for holes across the channel

- Boltzmann distribution of hole energy produces exponential decrease in channel conductance with gate voltage

#### Voltage-dependent quantal release

- K<sup>+</sup>/Na<sup>+</sup> through postsynaptic membrane

- Presynaptic membrane voltage controls energy barrier for neurotransmitter release

- Boltzmann distribution in quantal release energy produces exponential dependence of postsynaptic K<sup>+</sup>/Na<sup>+</sup> conductance

## Why Develop "Neural" Silicon Chips?

#### **Biology Motives:**

- *In silico* emulation of neural and sensory-motor systems

- Real-time computational power

- Accounts for noise and imprecision in neural elements

- Analysis by synthesis

- Emulating form and structure of neural systems provides better understanding, accounting for physical and architectural constraints

- Interfacing silicon with neurons and synapses *in vivo*

- Allows to observe and control neural and synaptic activity

#### **Engineering Motives:**

- Efficiency of implementation

- · Lower power, smaller size

- Real-world interface

- Integrated sensors and actuators

- Analog, continuous-time dynamics

- Intelligent brain-machine interfaces!

## **Neuromorphic Systems Design Flow**

#### **Neural Model**

Circuit Design and Simulation

Chip Layout

Microfabrication

http://www.mosis.org

Microchip(s)

**Chip Testing**

**System Integration**

**Neuromorphic System**

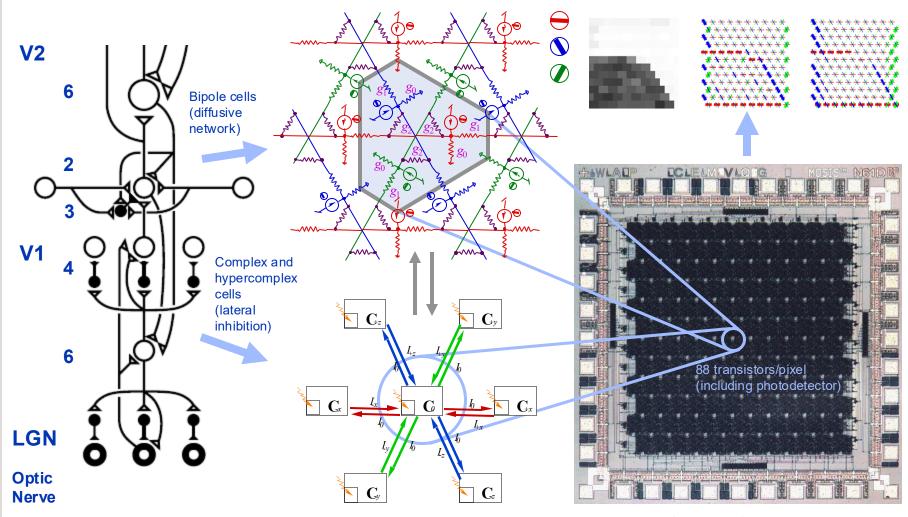

## Silicon Model of Visual Cortical Processing

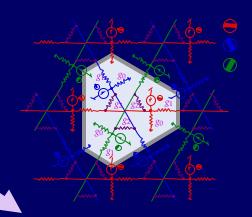

Neural model of boundary contour representation in V1, one orientation shown (Grossberg, Mingolla, and Williamson, 1997) Single-chip focal-plane implementation (Cauwenberghs and Waskiewicz, 1999)

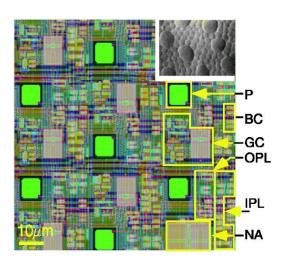

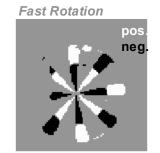

## **Event-Coding Silicon Retina**

Zaghloul and Boahen, 2006

- Models coding and communication of visual events in the mammalian retina and optic nerve

- Integrated photosensors (rods)

- On and off transient and sustained ganglia cell outputs

- Spatiotemporal compressed coding and communication in optic nerve

- Address-event coding of spikes

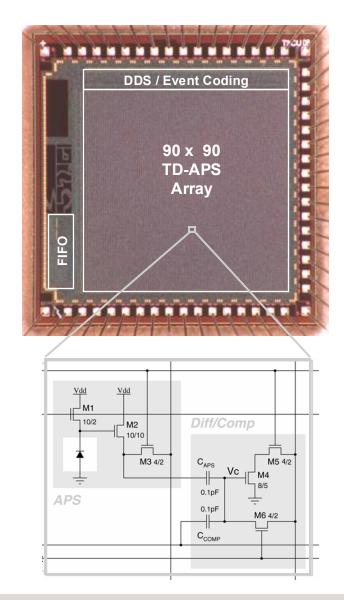

## **Change Threshold Detection APS CMOS Imager**

Chi, Mallik, Clapp, Choi, Cauwenberghs and Etienne-Cummings (2007)

- Event-driven video compression

- Change detection and threshold encoding on the focal plane

- 6T pixel combines APS and change event coding

- 4.3mW power at 3V and 30fps

Video Out

Change Events Out

## Reconfigurable Synaptic Connectivity and Plasticity

From Microchips to Large-Scale Neural Systems

Address-Event Representation

Synaptic

Plasticity &

Wiring

## **Scaling of Task and Machine Complexity**

Achieving (or surpassing) human-level machine intelligence requires a convergence between:

- Advances in computing resources approaching connectivity and energy efficiency levels of computing and communication in the brain;

- Advances in deep learning methods, and supporting data, to adaptively reduce algorithmic complexity.

## **Scaling and Complexity Challenges**

- Scaling the event-based neural systems to performance and efficiency approaching that of the human brain will require:

- Scalable advances in silicon integration and architecture

- Scalable, locally dense and globally sparse interconnectivity

- Hierarchical address-event routing

- Incrarement undress-coeffi routing

- High density (10<sup>12</sup> neurons, 10<sup>15</sup> synapses within 5L volume)

- Silicon nanotechnology and 3-D integration

- High energy efficiency (10<sup>15</sup> synOPS/s at 15W power)

- Adiabatic switching in event routing and synaptic drivers

- Scalable models of neural computation and synaptic plasticity

#### Neuro CS

EE

NanoE

**Phys**

CogSci

- Convergence between cognitive and neuroscience modeling

- Modular, neuromorphic design methodology

- Data-rich, environment driven evolution of machine complexity

### Large-Scale Reconfigurable Neuromorphic Computing

#### Technology and Performance Metrics

|                                   | Stromatias 2013<br>SpiNNaker<br>Manchester | Davies 2018<br>Loihi<br>Intel              | Merolla 2014<br>TrueNorth<br>IBM | Schemmel 2010<br>FACETS/BrainScaleS<br>Heidelberg | Benjamin 2014<br>NeuroGrid<br>Stanford       | Park 2014<br>IFAT<br>UCSD                  |

|-----------------------------------|--------------------------------------------|--------------------------------------------|----------------------------------|---------------------------------------------------|----------------------------------------------|--------------------------------------------|

| Technology (nm)                   | 130                                        | 14                                         | 28                               | 180                                               | 180                                          | 90                                         |

| Die Size (mm²)                    | 102                                        | 60                                         | 430                              | 50                                                | 168                                          | 16                                         |

| Neuron Type                       | Digital<br>Arbitrary                       | Digital<br>Conductance<br>Integrate & Fire | Digital<br>Accumulate & Fire     | Analog<br>Conductance<br>Integrate & Fire         | Analog<br>Shared-Dendrite<br>Conductance I&F | Analog<br>2-Compartment<br>Conductance I&F |

| # Neurons                         | 5216 <sup>1</sup>                          | 128k <sup>2</sup>                          | 1M <sup>2</sup>                  | 512                                               | 65k                                          | 65k                                        |

| <b>Neuron Area</b> (μm²)          | N/A <sup>1</sup>                           | 240 (240k) <sup>2</sup>                    | 14 (3325) <sup>2</sup>           | 1500                                              | 1800                                         | 140                                        |

| Peak Throughput<br>(Events/s)     | 5M                                         | 3.4G                                       | 1G                               | 65M                                               | 91M                                          | 73M                                        |

| Energy Efficiency<br>(J/SynEvent) | 8n                                         | 24p                                        | 26p                              | N/A                                               | 31p                                          | 22p                                        |

<sup>&</sup>lt;sup>1</sup> Software-instantiated neuron model

Benjamin, B., P. Gao, E. McQuinn, S. Choudhary, A. Chandrasekaran, J. Bussat, R. Alvarez-Icaza, J. Arthur, P. Merolla, and K. Boahen, "Neurogrid: A mixed analog-digital multichip system for large-scale neural simulations," *Proc. IEEE*, 102(5):699–716, 2014.

Davies, M. et al., "Loihi: A Neuromorphic Manycore Processor with On-Chip Learning," IEEE Micro, vol. 38 (1), pp. 82-99, 2018.

Merolla, P.A., J.V. Arthur, R. Alvarez-Icaza, A S. Cassidy, J. Sawada, F. Akopyan, B.L. Jackson, N. Imam, C. Guo, Y. Nakamura, B. Brezzo, I. Vo, S.K. Esser, R. Appuswamy, B. Taba, A. Amir, M.D. Flickner, W.P. Risk, R. Manohar, and D. S. Modha, "A million spiking-neuron integrated circuit with a scalable communication network and interface," *Science*, 345(6197):668–673, 2014.

Park, J., S. Ha, T. Yu, E. Neftci, and G. Cauwenberghs, "65k-neuron 73-Mevents/s 22-pJ/event asynchronous micro-pipelined integrate-and-fire array transceiver," Proc. 2014 IEEE Biomedical Circuits and Systems Conf. (BioCAS), 2014.

Schemmel, J., D. Bruderle, A. Grubl, M. Hock, K. Meier, and S. Millner, "A waferscale neuromorphic hardware system for large-scale neural modeling," *Proc. 2010 IEEE Int. Symp. Circuits and Systems (ISCAS)*, 1947–1950, 2010.

Stromatias, E., F. Galluppi, C. Patterson, and S. Furber, "Power analysis of largescale, real-time neural networks on SpiNNaker," *Proc. 2013 Int. Joint Conf. Neural Networks (IJCNN)*, 2013.

<sup>&</sup>lt;sup>2</sup> Time-multiplexed neuron processor

## Large-Scale Reconfigurable Neuromorphic Computing

"CRI: CI-NEW: Trainable Reconfigurable Development Platform for Large-Scale Neuromorphic Cognitive Computing," National Science Foundation CNS-1823366, G. Cauwenberghs (PI), E. Neftci, and A. Majumdar, 8/2018-7/2021.

Provides open access to large-scale reconfigurable neuromorphic computing hardware and software as an experimental testbed and development platform with up to 128M neurons and 32B synapses for the research community at large.

Neural-Synaptic Array Transceiver (Detorakis et al, Frontiers in Neuroscience, 2018)

NeuroDyn (2021 Telluride Neuromorphic Workshop)

## Closing the Loop: Interactive Neural/Artificial Intelligence

Neuromorphic Engineering

Adaptive Sensory Feature Extraction and Pattern Recognition

## Neuro Bio

Learning & Adaptation

Micropower

Mixed-Signal

VLSI

Neurosystems Engineering Biosensors, Neural Prostheses and Brain Interfaces

#### **Computational Systems Neuroscience**

#### **Neuromorphic Systems Engineering**

F. Broccard, S. Joshi, J. Wang and G Cauwenberghs, "Neuromorphic neural interfaces: from neurophysiological inspiration to biohybrid coupling with nervous systems," JNE, 2017

## Integrated Systems Neuroengineering

Neuromorphic/ Neurosystems Engineering

Neural Systems

## Silicon Neurons

Hodgkin-Huxley neuronal dynamics Integrate-and-fire models Action potentials as address events

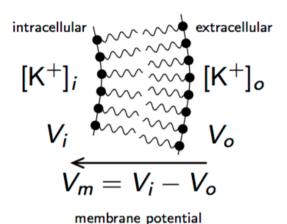

#### **Nernst Potentials**

$$\frac{[\mathsf{K}^+]_o}{[\mathsf{K}^+]_i} = \frac{n_o}{n_i} = e^{-\frac{\mathcal{E}_o - \mathcal{E}_i}{kT}} \left(= e^{-\frac{U_o - U_i}{RT}}\right)$$

Boltzman absolute gas constant temperature

$$= e^{-\frac{V_o - V_i}{kT/q}}$$

charge per molecule gas constant constant temperature

$$= 1.6 \ 10^{-19} \text{C} \text{ per valence index}$$

$$\Rightarrow E_{rest} = V_m|_{equilibrium} = \underbrace{\frac{kT}{q}}_{\text{Extracellular}} \ln \frac{[K^+]_o}{[K^+]_i} \\ = \underbrace{\frac{kT}{q} \ln 10}_{\text{Extracellular}} \log_{10} \frac{[K^+]_o}{[K^+]_i}$$

(mV) Ion (mM) (mM) Ioni 12 12 Na<sup>+</sup> 145 +67 $K^+$ 155 0.026 -981.5 100 nM 15,000 +129 $CI^-$ 123  $4.2^{b}$  $29^{b}$  $-90^{b}$

potential<sup>a</sup>

lon<sub>o</sub>

concentration

BENG 260 Neurodynamics — <a href="http://isn.ucsd.edu/courses/beng260">http://isn.ucsd.edu/courses/beng260</a>

concentration

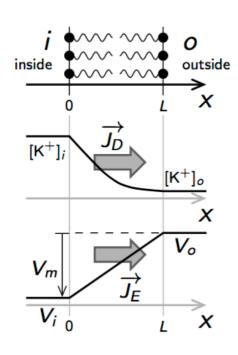

## **Nernst-Planck Equilibrium**

Equilibrium between **diffusion** and **drift**:

(chemical) (electrical)

**Diffusion:**

$$\overrightarrow{J_D} = qD \cdot \left( -\overrightarrow{\nabla} [\mathsf{K}^+] \right)$$

$$\Rightarrow \overrightarrow{J_{\mathsf{K}^+}} = \overrightarrow{J_D} + \overrightarrow{J_E} = 0$$

equilibrium

$$\Rightarrow -qD\frac{d[\mathsf{K}^+]}{dx} - q\mu[\mathsf{K}^+]\frac{dV}{dx} = 0 \ \Rightarrow \ \frac{D}{\mu}\left(\underbrace{\frac{d[\mathsf{K}^+]}{[\mathsf{K}^+]}}\right) = -dV_{d\left(\ln{[\mathsf{K}^+]}\right)} = -$$

$$\Rightarrow rac{D}{\mu} \ln rac{[\mathsf{K}^+]_o}{[\mathsf{K}^+]_i} = -(V_o - V_i) = V_m = E_{rest} ext{ with } rac{D}{\mu} = rac{kT}{q}$$

indeed,

$$D = \frac{kT}{q} \cdot \mu$$

Dissipation-fluctuation

(Einstein)

BENG 260 Neurodynamics — <a href="http://isn.ucsd.edu/courses/beng260">http://isn.ucsd.edu/courses/beng260</a>

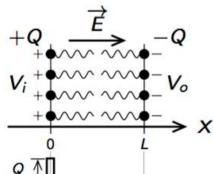

## **Membrane Capacitance**

capacitance = differential charge accumulation with voltage across insulator (membrane)

Charge Density  $\rho$   $\xrightarrow{\frac{Q}{A}}$   $\rightarrow x$  Electric  $\overrightarrow{E}$   $\xrightarrow{\frac{1}{\varepsilon}Q}$   $\xrightarrow{\frac{1}{\varepsilon}A}$   $\rightarrow x$

$$\overrightarrow{\nabla}\overrightarrow{E} = \frac{\rho}{\varepsilon}$$

, or  $\frac{dE}{dx} = \frac{\rho}{\varepsilon}$

Potential

$$V$$

$$\begin{array}{c}

V_i \\

\hline

V_m = \frac{LQ}{\varepsilon A} \\

\hline

V_o

\end{array}$$

$\overrightarrow{\nabla} V = -\overrightarrow{E}$ , or  $\frac{dV}{dx} = -E$

$$Q = C_m \cdot V_m$$

with  $C_m = \varepsilon \cdot \frac{A}{L}$   $\frac{\varepsilon}{L} \approx 0.01 \text{ F/m}^2$

BENG 260 Neurodynamics — <a href="http://isn.ucsd.edu/courses/beng260">http://isn.ucsd.edu/courses/beng260</a>

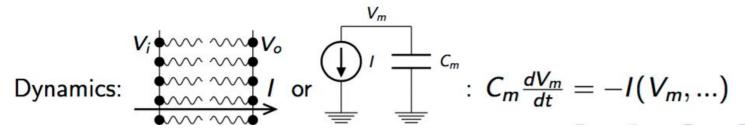

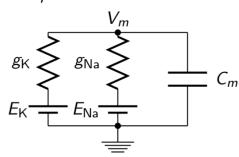

#### **Membrane Conductance**

$$\begin{array}{c|c}

\hline

& V_m \\

\hline

& g_K \\

\hline

& g_{Na} \\

\hline

& F_{Na} \\

\hline

& G_m

\end{array}$$

Equilibrium:  $E_{rest} = V_m = \frac{g_K E_K + g_{Na} E_{Na}}{g_K + g_{Na}}$

Not quite...

$$E_{rest} = V_m = \frac{kT}{q} \ln \frac{\mu_K[K]_o + \mu_{Na}[Na]_o}{\mu_K[K]_i + \mu_{Na}[Na]_i}$$

BENG 260 Neurodynamics — http://isn.ucsd.edu/courses/beng260

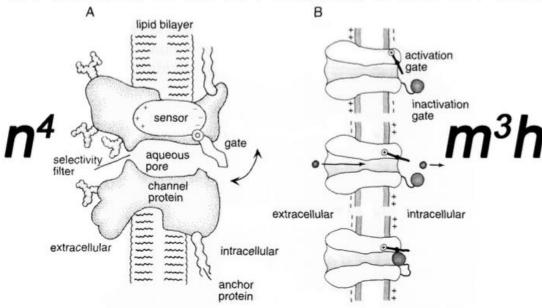

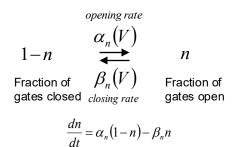

## **Voltage Gated Ion Channels**

n: slow K+ activation; m: fast Na+ activation; h: slow Na+ inactivation

Figure 5.8 Gating of membrane channels. In both figures, the interior of the neuron is to the right of the membrane, and the extracellular medium is to the left. (A) A cartoon of gating of a persistent conductance. A gate is opened and closed by a sensor that responds to the membrane potential. The channel also has a region that selectively allows ions of a particular type to pass through the channel, for example, K+ ions for a potassium channel. (B) A cartoon of the gating of a transient conductance. The activation gat is coupled to a voltage sensor (denoted by a circled +) and acts like the gate in A. A second gate, denoted by the ball, can block that channel once it is open. The top figure shows the channel in a deactivated (and deinactivated) state. The middle panel shows an activated channel, and the bottom panel shows an inactivated channel. Only the middle panel corresponds to an open, ion-conducting state. (A from Hille, 1992; B from Kandel et al., 1991.)

Dayan & Abbott 2001, p. 169

BENG 260 Neurodynamics — <a href="http://isn.ucsd.edu/courses/beng260">http://isn.ucsd.edu/courses/beng260</a>

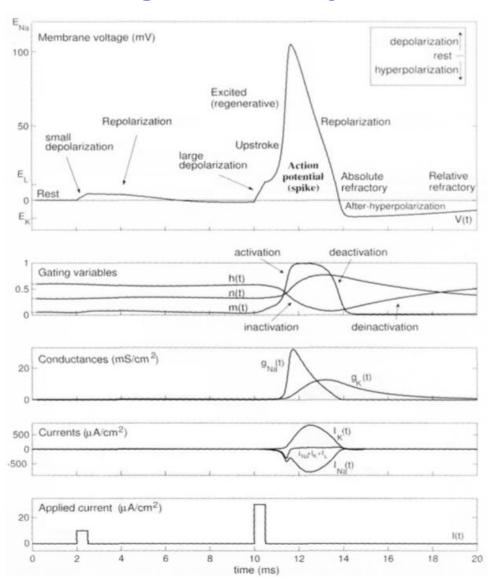

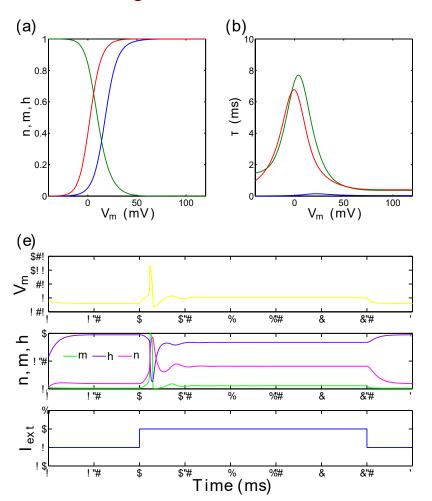

## **Hodgkin-Huxley Model**

#### Squid axon:

$$C_{m} \frac{dV_{m}}{dt} = I_{ext} - \underline{\bar{g}}_{K} n^{4} (V_{m} - E_{K}) - \underline{\bar{g}}_{Na} m^{3} h (V_{m} - E_{Na}) - \underline{g}_{L} (V_{m} - E_{L})$$

$$I_{K} I_{Na} I_{L}$$

$$E_{K} = -12 \, mV E_{Na} = 120 \, mV E_{L} = 10.6 \, mV$$

$$\bar{g}_{K} = 36 \, mS/cm^{2} g_{Na} = 120 \, mS/cm^{2} g_{L} = 0.3 \, mS/cm^{2}$$

$$(mS = \mu A/mV)$$

$$\begin{array}{lll} \frac{dn}{dt} = & \alpha_{n}(1-n) - \beta_{n}n = & \frac{n_{\infty}-n}{\tau_{n}}; & \alpha_{n}(V_{m}) = & \frac{10-V_{m}}{100(e^{1-V_{m}/10}-1)}; & \beta_{n}(V_{m}) = & \frac{1}{8}e^{-V_{m}/80} \\ \frac{dm}{dt} = & \alpha_{m}(1-m) - \beta_{m}m = & \frac{m_{\infty}-m}{\tau_{m}}; & \alpha_{m}(V_{m}) = & \frac{25-V_{m}}{100(e^{2.5-V_{m}/10}-1)}; & \beta_{m}(V_{m}) = & 4e^{-V_{m}/18} \\ \frac{dh}{dt} = & \alpha_{h}(1-h) - \beta_{h}h = & \frac{h_{\infty}-h}{\tau_{h}}; & \alpha_{h}(V_{m}) = & \frac{7}{100}e^{-V_{m}/20}; & \beta_{h}(V_{m}) = & \frac{1}{1+e^{3-V_{m}/10}} \end{array}$$

$\alpha_x$  and  $\beta_x$  in units 1/ms;  $V_m$  in units mV\*  $V_m$  slightly shifted by 65mV so that  $E_{rest} \equiv 0mV$

Hodgkin & Huxley, 1952

BENG 260 Neurodynamics — <a href="http://isn.ucsd.edu/courses/beng260">http://isn.ucsd.edu/courses/beng260</a>

# **Hodgkin-Huxley Model**

Izhikevich 2007, p. 40

BENG 260 Neurodynamics — <a href="http://isn.ucsd.edu/courses/beng260">http://isn.ucsd.edu/courses/beng260</a>

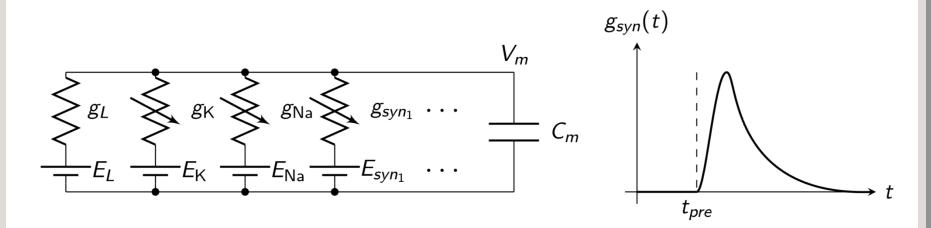

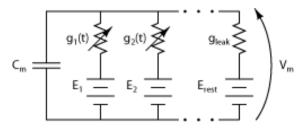

# **Postsynaptic Conductance**

Postsynaptic membrane current and voltage:

$$C_m rac{dV_m}{dt} = I_{ext} - I_{K} - I_{Na} - I_{L} - \sum_i I_{syn_i}$$

$I_{syn_i} = g_{syn_i}(t) \cdot (V_m - E_{syn_i})$

BENG 260 Neurodynamics — <a href="http://isn.ucsd.edu/courses/beng260">http://isn.ucsd.edu/courses/beng260</a>

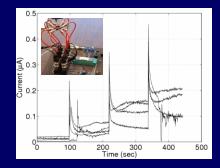

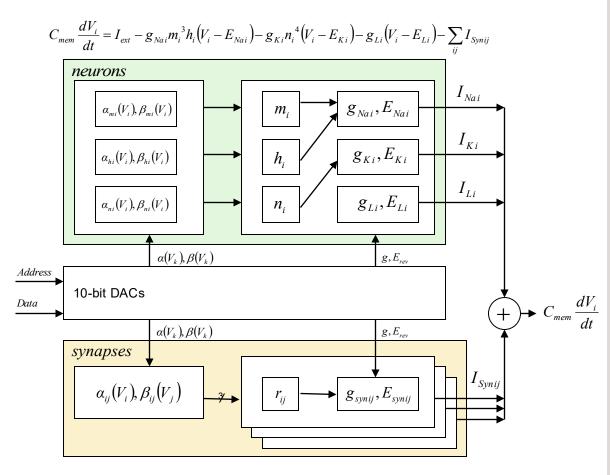

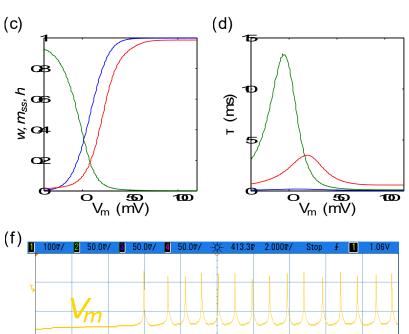

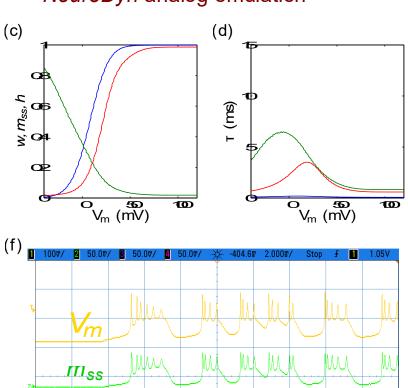

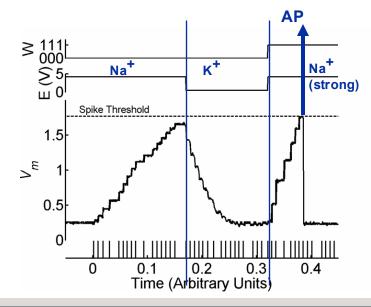

#### NeuroDyn: Biophysical Neurodynamics in Analog VLSI

Yu and Cauwenberghs 2009

Generalized Hodgkin-Huxley neural and conductance-based synapse membrane dynamics in silico:

The NeuroDyn chip emulates detailed neural and synaptic dynamics in silicon by implementing rate-based models of voltage-gated and ligand-gated channel kinetics.

Each parameter is individually addressable and programmable through 10-bit DACs.

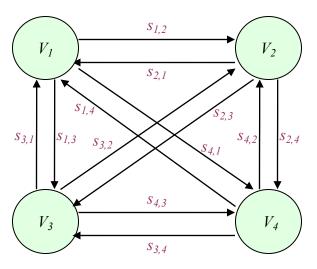

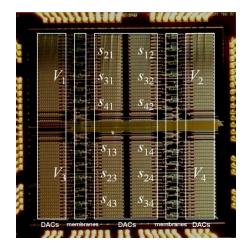

#### NeuroDyn: Biophysical Neurodynamics in Analog VLSI

Yu and Cauwenberghs 2009

Programmable Parameters: 384 total

| Neurons $V_i$ $\alpha_{n_i}(V)$ $m_i$ $h_i$                          | β <sub><b>n</b>i</sub> (V)<br>mi<br>h: | g <sub>Na;</sub><br>K;               | E <sub>Na;</sub><br>K;               |

|----------------------------------------------------------------------|----------------------------------------|--------------------------------------|--------------------------------------|

| 4x3x7*                                                               | 4x3x7*                                 | 4x3                                  | 4x3                                  |

| Synapses ${ m s}_{ij} = { m c}_{r_{ij}}({ m V}_{pre}) = { m 12x7}^*$ | $eta_{r_{ij}}(V_{post}) \ 12x7^*$      | g <sub>syn<sub>ij</sub><br/>12</sub> | E <sub>syn<sub>ij</sub><br/>12</sub> |

\*All rates  $\alpha$ ,  $\beta$  are 7-point sigmoidal spline regression functions  $\alpha$  ( $V_k$ ),  $\beta$  ( $V_k$ ), k = 1,...7

The *NeuroDyn* Board consists of 4 neurons fully connected through 12 synapses. All parameters are individually programmable and have biophysically-based parameters governing the conductances, reversal potentials, and voltage-dependance of the channel kinetics.

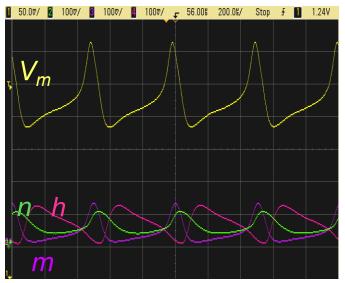

Recorded dynamics of action potential and channel kinetics for one HH neuron.

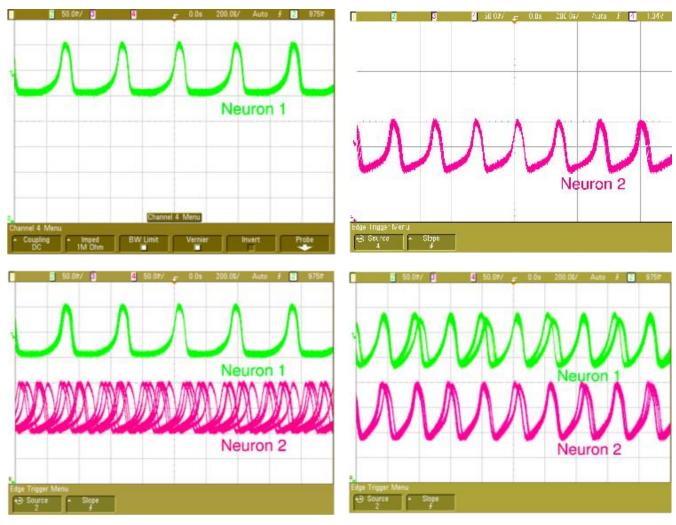

# NeuroDyn Synaptic Coupling

Uncoupled

Mutual inhibitory synaptic coupling

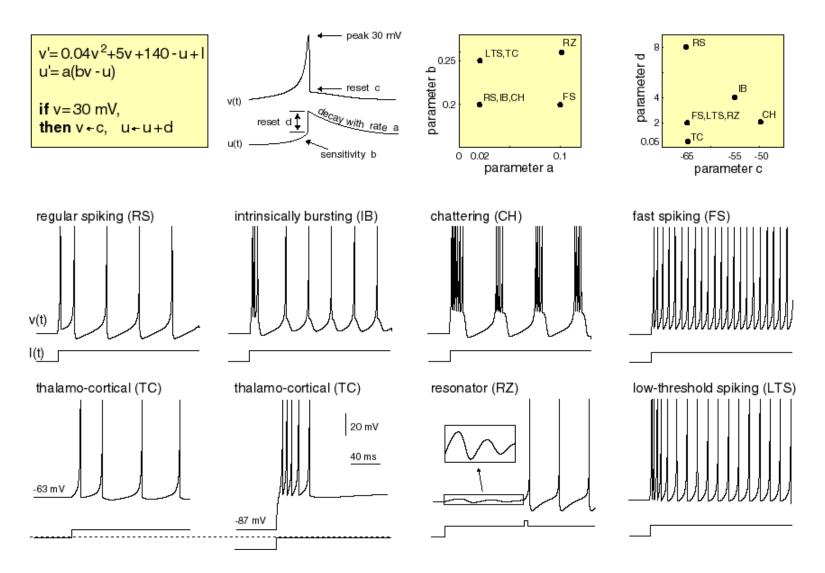

# **Generalized Map-Based I&F Neural Dynamics**

Izhikevich 2003; Rulkov, Timofeev & Bazhenov 2004; Mihalas & Niebur 2009

Electronic version of the figure and reproduction permissions are freely available at www.izhikevich.com

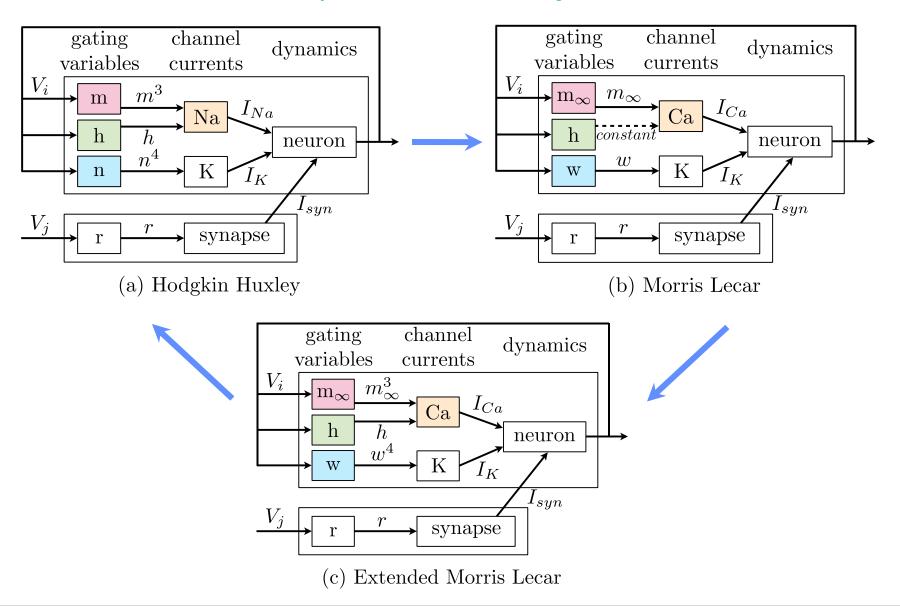

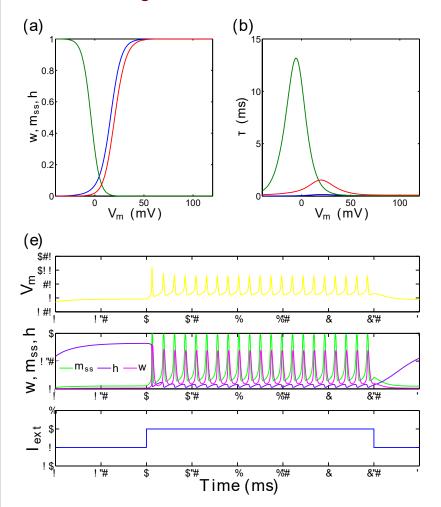

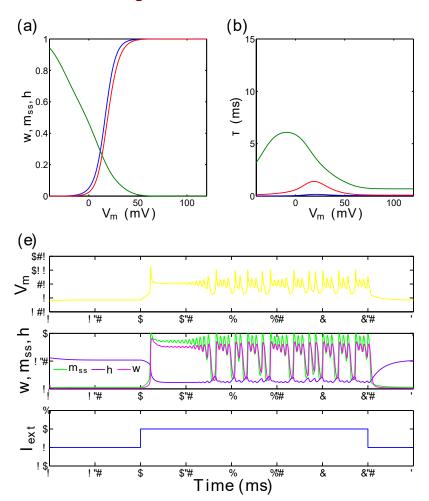

# **Generalized HH/ML Neural Dynamics**

Yu, Sejnowski, and Cauwenberghs 2010

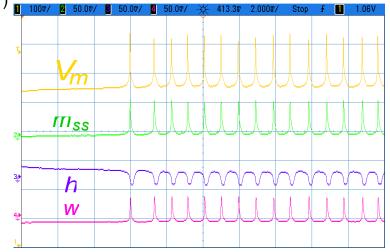

# NeuroDyn Tonic Spiking

#### Matlab digital simulation

#### NeuroDyn analog emulation

Yu, Sejnowski, and Cauwenberghs 2011

# NeuroDyn Phasic Spiking

#### Matlab digital simulation

#### NeuroDyn analog emulation

Yu, Sejnowski, and Cauwenberghs 2011

# **NeuroDyn** Tonic Bursting

#### Matlab digital simulation

#### NeuroDyn analog emulation

Yu, Sejnowski, and Cauwenberghs 2011

W

### Reconfigurable Synaptic Connectivity and Plasticity

From Microchips to Large-Scale Neural Systems

Address-Event Representation

Synaptic

Plasticity &

Wiring

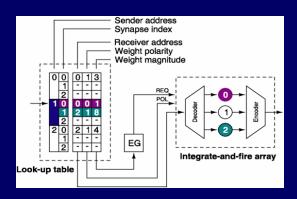

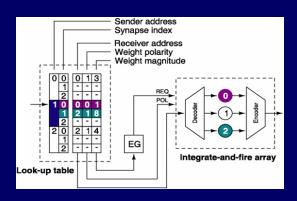

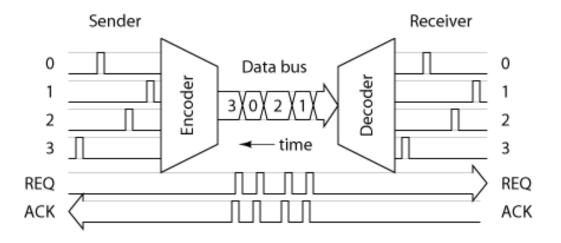

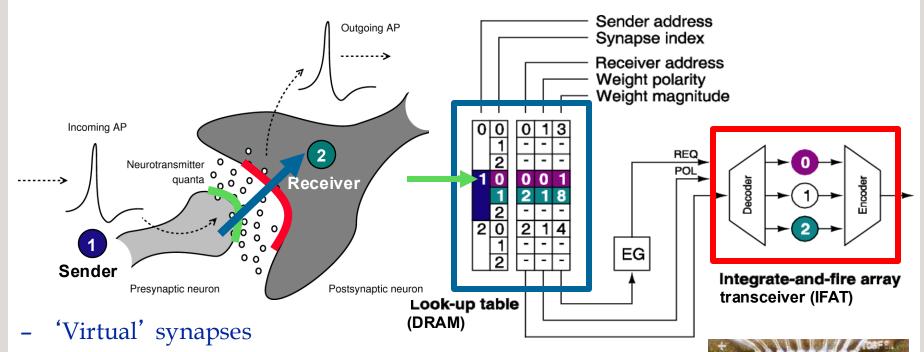

### **Address-Event Representation (AER)**

Lazzaro et al., 1993; Mahowald, 1994; Deiss 1994; Boahen 2000

- AER emulates extensive connectivity between neurons by communicating spiking events time-multiplexed on a shared data bus.

- Spikes are represented by two values:

- Cell location (address)

- Event time (implicit)

- All events within Δt are "simultaneous"

### **Address-Event Synaptic Connectivity**

Goldberg, Cauwenberghs and Andreou, 2000

- Dynamically reconfigurable

- Wide-ranging connectivity

- Rewiring and synaptic plasticity

- Quantal release: R = n p q

- n: multiplicity

(repeat event)

- p: probability of release

- (toss a coin)

- q: quantity released

- (set amplitude)

IFAT2 (2000)

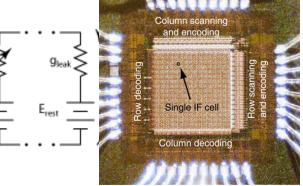

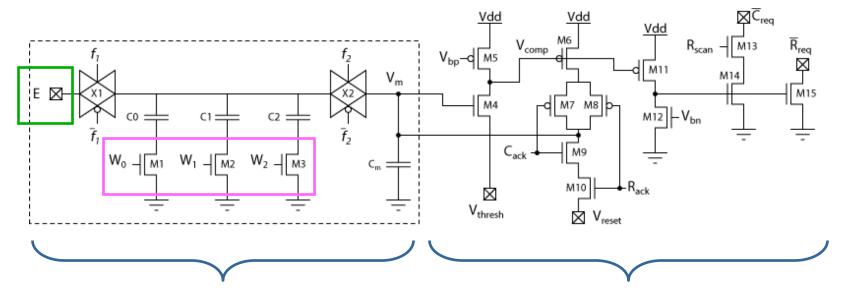

### Silicon Membrane Array Transceiver

Vogelstein, Mallik and Cauwenberghs, 2004

- Voltage-controlled membrane conductance

- Event-driven activation

- Dynamically reconfigurable:

- conductance g

- driving potential E

Address-event encoding of pre-and post-synaptic action potentials

IFAT3 (2004)

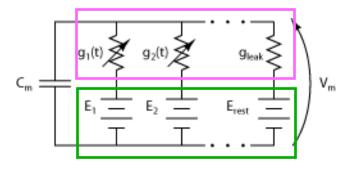

#### **Silicon Membrane Circuit**

Goldberg, Cauwenberghs and Andreou, 2000 Vogelstein, Mallik and Cauwenberghs, 2004

$g_i(t)$  ion-specific membrane conductance

*E<sub>i</sub> ion-specific* reversal potential

Synapse subcircuit

Action potential generation and AER handshaking

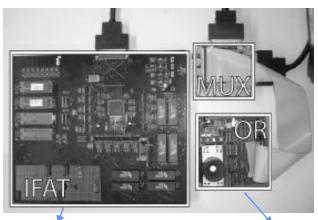

### Hierarchical Vision and Saliency-Based Acuity Modulation

Vogelstein, Mallik, Culurciello, Cauwenberghs, and Etienne-Cummings, NECO 2007

**IFAT** Cortical Model

4800 silicon neurons 4,194,304 synapses Octopus Silicon Retina

80 x 60 pixels

AER spiking output

**OR** image

Simple cell response

Saliency map

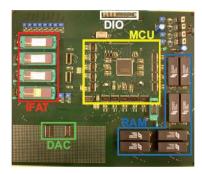

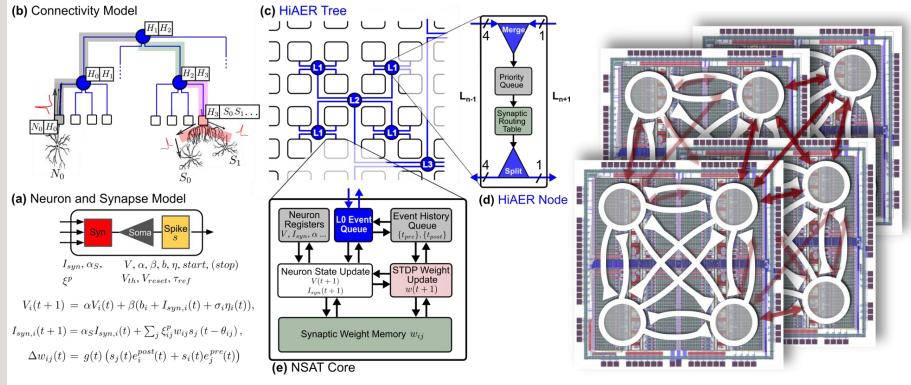

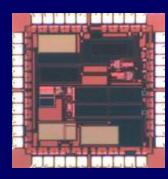

### Large-Scale Reconfigurable Neuromorphic Computing

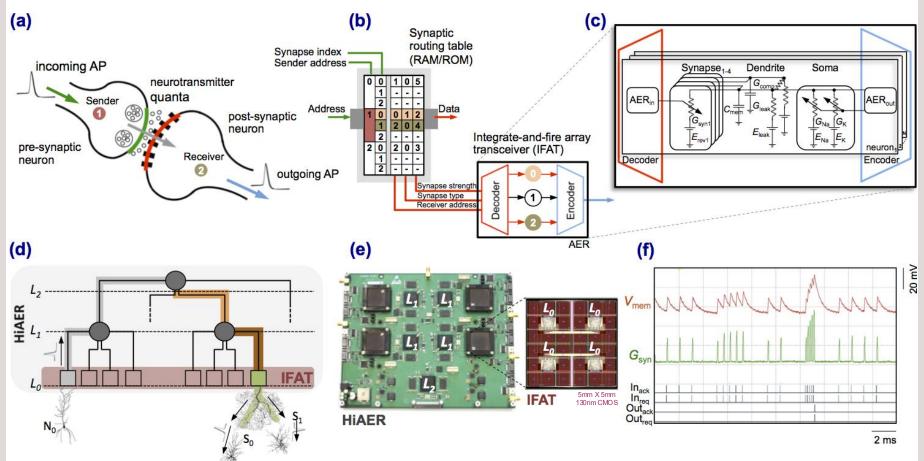

Hierarchical Address-Event Routing (HiAER) Integrate-and-Fire Array Transceiver (IFAT) for scalable and reconfigurable neuromorphic neocortical processing. (a) Biophysical model of neural and synaptic dynamics. (b) Dynamically reconfigurable synaptic connectivity is implemented across IFAT arrays of addressable neurons by routing neural spike events locally through DRAM synaptic routing tables. (c) Each neural cell models conductance based membrane dynamics in proximal and distal compartments for synaptic input with programmable axonal delay, conductance, and reversal potential. (d) Multiscale global connectivity through a hierarchical network of HiAER routing nodes. (e) HiAER-IFAT board with 4 IFAT custom silicon microchips, serving 256k neurons and 256M synapses, and spanning 3 HiAER levels (L0-L2) in connectivity hierarchy. (f) The IFAT neural array multiplexes and integrates (top traces) incoming spike synaptic events to produce outgoing spike neural events (bottom traces). The latest FAT microchip measured energy consumption is 22 pJ per spike event, several orders of magnitude more efficient than emulation on CPU/GPU platforms.

Yu et al, BioCAS 2012; Park et al, BioCAS 2014; Park et al, TNNLS 2017; Broccard et al, JNE 2017

### **BENG 216 Neuromorphic Integrated Bioelectronics**

| Date         | Topic                                                                                                                                                                                                                                                                   |  |

|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 9/29, 10/1   | Biophysical foundations of natural intelligence in neural systems. Subthreshold MOS silicon models of membrane excitability. Silicon neurons. Hodgkin-Huxley and integrate-and-fire models of spiking neuronal dynamics. Action potentials as address events.           |  |

| 10/6, 10/8   | Silicon retina. Low-noise, high-dynamic range photoreceptors. Focal-plane array signal processing. Spatial and temporal contrast sensitivity and adaptation. Dynamic vision sensors.                                                                                    |  |

| 10/13, 10/15 | Silicon cochlea. Low-noise acoustic sensing and automatic gain control. Continuous wavelet filter banks. Interaural time difference and level difference auditory localization. Blind source separation and independent component analysis.                             |  |

| 10/20, 10/22 | Silicon cortex. Neural and synaptic compute-in-memory arrays. Address-event decoders and arbiters, and integrate-and-fire array transceivers. Hierarchical address-event routing for locally dense, globally sparse long-range connectivity across vast spatial scales. |  |

| 10/27, 10/29 | Midterm review. Modular and scalable design for neuromorphic and bioelectronic integrated circuits and systems. Design for full testability and controllability.                                                                                                        |  |

| 11/3, 11/5   | Low-noise, low-power design. Fundamental limits of noise-energy efficiency, and metrics of performance. Biopotential and electrochemical recording and stimulation, lab-on-a-chip electrophysiology, and neural interface systems-on-chip.                              |  |

| 11/10, 11/12 | Adaptive offset cancelation and autoranging in dynamic vision sensing. Tobi Delbruck's lecture on silicon retina history with a live demo or event-based dynamic vision systems.                                                                                        |  |

| 11/17, 11/19 | Learning and adaptation to compensate for external and internal variability over extended time scales. Background blind calibration of device mismatch. Correlated double sampling and chopping for offset drift and low-frequency noise cancellation.                  |  |

| 11/24, 11/26 | Energy conservation. Resonant inductive power delivery and data telemetry. Ultra-high efficiency neuromorphic computing. Resonant adiabatic energy-recovery charge-conserving synapse arrays.                                                                           |  |

| 12/1 - 12/5  | Project final presentations. All are welcome!                                                                                                                                                                                                                           |  |